# UNIVERSITAS INDONESIA

# SIMULASI ERROR CORRECTION DENGAN PENGGABUNGAN TEKNIK REED-SOLOMON CODE (15,5) DAN BCH CODE (15,5) MENGGUNAKAN DSK TMS320C6713 BERBASIS SIMULINK

# **SKRIPSI**

# KHOTMAN HILMY FAJRIAN 0405030486

FAKULTAS TEKNIK PROGRAM STUDI TEKNIK ELEKTRO DEPOK JUNI 2010

# **UNIVERSITAS INDONESIA**

# SIMULASI ERROR CORRECTION DENGAN PENGGABUNGAN TEKNIK REED-SOLOMON CODE (15,5) DAN BCH CODE (15,5) MENGGUNAKAN DSK TMS320C6713 BERBASIS SIMULINK

# **SKRIPSI**

Diajukan sebagai salah satu syarat untuk memperoleh gelar Sarjana

# KHOTMAN HILMY FAJRIAN 0405030486

FAKULTAS TEKNIK

PROGRAM STUDI TEKNIK ELEKTRO

DEPOK

JUNI 2010

# HALAMAN PERNYATAAN ORISINALITAS

Skripsi ini adalah hasil karya saya sendiri, dan sumber baik yang dikutip maupun dirujuk telah saya nyatakan dengan benar.

Nama : KHOTMAN HILMY FAJRIAN

NPM : 0405030338

Tanda tangan:

Tanggal: 15 Juni 2010

#### HALAMAN PENGESAHAN

Skripsi ini diajukan oleh

Nama : Khotman Hilmy Fajrian

NPM : 0405030486 Program Studi : Teknik Elektro

Judul Skripsi : Simulasi Error Correction Dengan

Penggabungan Teknik Reed-Solomon Code (15,5) dan BCH Code (15,5) Menggunakan DSK

TMS320C6713 Berbasis Simulink

Telah berhasil dipertahankan di hadapan Dewan Penguji dan diterima sebagai bagian persyaratan yang diperlukan untuk memperoleh gelar Sarjana Teknik pada Program Studi Elektro, Fakultas Teknik Universitas Indonesia

# DEWAN PENGUJI

Pembimbing : Prof. Dr. Ir. Dadang Gunawan, M.Eng

Penguji : Dr. Ir. Arman D. Diponegoro

Penguji : Filbert Hilman Juwono, S.T., M.T.

Ditetapkan di : Depok Tanggal : 7 Juni 2010

# **KATA PENGANTAR**

Puji syukur saya panjatkan kepada Allah SWT, karena atas berkat dan rahmat-Nya, saya dapat menyelesaikan skripsi ini. Penulisan skripsi ini dilakukan dalam rangka memenuhi salah satu syarat untuk mencapai gelar Sarjana Teknik Jurusan Teknik Elektro pada Fakultas Teknik Universitas Indonesia. Saya menyadari bahwa tanpa bantuan dan bimbingan dari berbagai pihak, dari masa perkuliahan sampai pada penyusunan skripsi ini, sangatlah sulit bagi saya untuk menyelesaikan skripsi ini. Oleh karena itu, saya mengucapkan terima kasih kepada:

- (1) Prof. Dr. Ir. Dadang Gunawan, M.Eng dan Dr. Ir. Arman D. Diponegoro, selaku dosen pembimbing 1 dan 2 yang telah menyediakan waktu, tenaga, dan pikiran untuk mengarahkan saya dalam penyusunan tugas akhir ini;

- (2) Pihak laboratorium telekomunikasi Departemen Teknik Elektro yang telah banyak membantu dalam usaha memperoleh data dan peralatan yang saya perlukan;

- (3) Orang tua saya, ibunda dan ayahanda yang terus tanpa pernah lelah memberikan yang segala terbaik untukku, tak henti memberikan dorongan menuju keberhasilan tanpa pernah menuntut. Semoga Allah Ta'ala senantiasa melimpahkan rahmatNya kepada ayah dan ibu. Kakak dan adik tercinta, yang selalu mendukung dan ingin melihat saudaranya menggapai keberhasilan;

- (4) Teman setia penulis, Putri, yang tak pernah jemu mengingatkan penulis untuk tidak menyerah dalam menggapai cita-cita yang baik;

- (5) Teman-teman elektro dan semua pihak yang telah membantu dalam pembuatan dan penyusunan tugas akhir ini.

Akhir kata, saya berharap Allah SWT berkenan membalas segala kebaikan semua pihak yang telah membantu. Semoga skripsi ini dapat membawa manfaat bagi pengembangan ilmu.

Jakarta, 15 Juni 2010 Penulis

# LEMBAR PERNYATAAN PERSETUJUAN PUBLIKASI SKRIPSI UNTUK KEPENTINGAN AKADEMIS

Sebagai sivitas akademika Universitas Indonesia, saya yang bertanda tangan di bawah ini:

Nama : KHOTMAN HILMY FAJRIAN

NPM : 0405030486 Program Studi : Teknik Elektro Departemen : Teknik Elektro

Fakultas : Teknik Jenis karya : Skripsi

demi pengembangan ilmu pengetahuan, menyetujui untuk memberikan kepada Universitas Indonesia **Hak Bebas Royalti Nonekslusif** (*Non-exclusive Royalty-FreeRight*) atas karya ilmiah saya yang berjudul:

# SIMULASI ERROR CORRECTION DENGAN PENGGABUNGAN TEKNIK REED-SOLOMON CODE (15,5) DAN BCH CODE (15,5) MENGGUNAKAN DSK TMS320C6713 BERBASIS SIMULINK

beserta perangkat yang ada (jika diperlukan). Dengan Hak Bebas Royalti Nonekslusif ini, Universitas Indonesia berhak menyimpan, mengalihmedia/memformat-kan, mengelola dalam bentuk pangkalan data (database), merawat, dan mempublikasikan skripsi saya tanpa meminta izin dari saya selama tetap mencantumkan nama saya sebagai penulis/pencipta dan sebagai pemilik Hak Cipta.

Demikian pernyataan ini saya buat dengan sebenarnya.

Dibuat di : Jakarta Pada Tanggal : 15 Juni 2010 Yang menyatakan

(KHOTMAN HILMY FAJRIAN)

#### **ABSTRAK**

Nama : KHOTMAN HILMY FAJRIAN

Program Studi : Teknik Elektro

Judul : SIMULASI ERROR CORRECTION DENGAN

PENGGABUNGAN TEKNIK REED-SOLOMON CODE (15,5) DAN BCH CODE (15,5) MENGGUNAKAN DSK

TMS320C6713 BERBASIS SIMULINK

Skipsi ini membahas sebuah rancangan simulasi rangkaian pengoreksi kesalahan ( $error\ correction$ ) dalam sistem komunikasi digital menggunakan program simulasi Simulink. Metode yang digunakan untuk mendeteksi dan mengoreksi kesalahan adalah metode penyandian siklis dengan teknik penyandian BCH (Bose Chaudhury Hocquenhem)  $C_{\rm BCH}(n,k)$  dan RS (Reed-Solomon)  $C_{\rm RS}(n,k)$ . Kedua teknik tersebut digabungkan secara serial (concatetaned), dimana panjang kata sandi yang dipergunakan untuk penyandian RS adalah 15 simbol (digit) dan untuk BCH 15 bit. Sedangkan panjang informasinya, 5 simbol untuk penyandian RS dan kelipatan bulat k bit untuk BCH. Teknik RS (15,5) dapat memperbaiki kesalahan sebanyak 5 simbol secara acak, sedangkan teknik BCH (15,5) mampu memperbaiki 3 bit kesalahan secara acak. Dengan penggabungan kedua teknik tersebut dihasilkan rangkaian  $error\ correction$  yang mampu mengoreksi kesalahan acak sekitar 36 bit dan kesalahan mengelompok hingga 116 bit di belakang dan 43 bit di mana saja.

Rancangan simulasi penyandian ini kemudian diaplikasikan pada perangkat *signal* processing DSK6713 dengan cara memasukkan rancangan program simulink ke perangkat DSK tersebut melalui program *C6000 Code Composer Studio* versi 3.1. Dari hasil pengujian dengan menggunakan fasilitas RTDX didapat bahwa program yang dibuat dengan model simulink dapat berjalan dengan baik pada DSK6713 dan sesuai dengan simulasi pada program simulink.

Kata Kunci:

RS, BCH, Simulink, DSK6713, RTDX

#### **ABSTRACT**

Name : KHOTMAN HILMY FAJRIAN

Study Program : Electrical Engineering

Title : SIMULATION OF ERROR CORRECTION BY

COMBINING REED-SOLOMON CODE (15,5) AND BCH CODE (15,5) USING DSK TMS320C6713 BASED ON

SIMULINK MODEL

This thesis make a simulation design of an equipment for error correction in digital communication system using simulation program Simulink. The methode used to detect and correct the error is cyclic coding methode with BCH (Bose Chaudhury Hocquenhem) Code  $C_{\rm BCH}(n,k)$  and RS (Reed-Solomon) Code  $C_{\rm RS}(n,k)$  technique. Both the technique are combined in serial configuration (concatenated). For RS code we use 15 symbols (digits) codeword and 5 symbols information length. Whereas for BCH code we use 15 bits codeword and integer multiple of k bits information length. RS code (15,5) can correct 5 symbols random error and BCH code (15,5) can correct 3 bits random error. By combining the techniques obtained an error correction circuit that can correct up to about 36 bits of random error and up to 116 bits in rear and 43 bits anywhere of burst error.

Simulation design of this coding then will be aplicated on signal processing equipment of DSK6713 by injecting the simulation program designed by simulink to the DSK using program C6000 Code Composer Studio version 3.1. From the result of the simulation testing using RTDX obtained that the program designed by simulink can be executed properly on DSK6713 and is suitable with the result of simulation on simulink.

Keyword:

RS, BCH, Simulink, DSK6713, RTDX

# **DAFTAR ISI**

| I                                                                                                       | Halaman |

|---------------------------------------------------------------------------------------------------------|---------|

| HALAMAN JUDUL                                                                                           | i       |

| HALAMAN PERNYATAAN ORISINALITAS                                                                         | ii      |

| LEMBAR PENGESAHAN                                                                                       | iii     |

| KATA PENGANTAR                                                                                          | iv      |

| LEMBAR PERSETUJUAN PUBLIKASI KARYA ILMIAH                                                               | v       |

| ABSTRAK                                                                                                 | vi      |

| ABSTRACT                                                                                                | vii     |

| DAFTAR ISI                                                                                              | viii    |

| DAFTAR GAMBAR                                                                                           |         |

| DAFTAR TABEL                                                                                            | xi      |

| BAB 1 PENDAHULUAN                                                                                       |         |

| 1.1 LATAR BELAKANG                                                                                      |         |

| 1.2 PERUMUSAN MASALAH                                                                                   |         |

| 1.3 TUJUAN                                                                                              |         |

| 1.4 BATASAN MASALAH                                                                                     |         |

| 1.5 SISTEMATIKA PENULISAN                                                                               |         |

| BAB 2 PENYANDIAN SIKLIS DAN DSK TMS320C6713                                                             |         |

| 2.1 KONSEP PENYANDIAN SIKLIS                                                                            |         |

| 2.2 POLINOMIAL GENERATOR DAN <i>PARITY CHECK</i> PADA                                                   |         |

| PENYANDIAN SIKLIS                                                                                       | A 5     |

| 2.3 PROSES PENYANDIAN (ENCODING)                                                                        |         |

| 2.4 PROSES PENGURAIAN (DECODING)                                                                        |         |

| 2.5 PENYANDIAN DAN PENGURAIAN PADA TEKNIK                                                               | /       |

| PENYANDIAN SIKLIS BCH DAN RS                                                                            | Q       |

| 2.5.1 Bose Chaudhury Hocquenhem (BCH)                                                                   |         |

| 2.5.2 Reed-Solomon (RS)                                                                                 |         |

| 2.5.3 Penggabungan Reed-Solomon (7,5) Dengan BCH (15,5)                                                 |         |

| 2.5.3 Fenggabungan Reed-Solomon (7,5) Dengan BCH (15,5) 2.6 DIGITAL SIGNAL PROCESSING STARTER KIT (DSK) | )) 10   |

| TMS320C6713                                                                                             | 17      |

| 2.6.1 Digital Signal Processing Starter Kit (DSK) Prosesor.                                             |         |

|                                                                                                         |         |

|                                                                                                         |         |

| 2.6.3 Starting DSK TMS320C6713 BAB 3 PERANCANGAN SIMULASI                                               | 20      |

|                                                                                                         |         |

| 3.1 SIMULINK                                                                                            | 21      |

|                                                                                                         |         |

| 3.1.2 Blok "Encoder RS (15,5) Masukan Integer"                                                          |         |

| 3.1.3 Blok "Encoder BCH (15,5)"                                                                         | 24      |

| 3.1.4 Blok "Channel (Penyisipan Error)"                                                                 |         |

| 3.1.5 Blok " <i>Decoder</i> BCH (15,5)"                                                                 |         |

| 3.1.6 Blok "Decoder RS (15,5) Keluaran Integer"                                                         |         |

| 3.1.7 Blok "Perhitungan BER" dan "Perhitungan SER"                                                      |         |

| 3.2 PENERAPAN MODEL SIMULINK KE DSK TMS320C6713 .                                                       |         |

| BAB 4 PENGUJIAN DAN ANALISIS SISTEM                                                                     | 35      |

| 4.1 PERBANDINGAN HASIL UJI SIMULINK                                                                     |         |

| TERHADAP HASIL PERHITUNGAN MANUAL                                                                       | 35      |

| 4.2 PENGUJIAN DENGAN SIMULINK              | 38 |

|--------------------------------------------|----|

| 4.2.1 Pola Kesalahan Mengelompok           | 38 |

| 4.2.2 Pola Kesalahan Menyebar              |    |

| 4.3 PENGUJIAN DENGAN DSK TMS320C6713       |    |

| 4.4 PERBANDINGAN HASIL UJI DSK DENGAN RTDX |    |

| TERHADAP HASIL UJI SIMULINK                | 49 |

| BAB 5 KESIMPULAN                           | 51 |

| DAFTAR REFERENSI                           | 52 |

| LAMPIRAN                                   | 53 |

# **DAFTAR GAMBAR**

| Halaman                                                                 |

|-------------------------------------------------------------------------|

| Gambar 1.1 Diagram blok sistem transmisi atau penyimpanan data          |

| Gambar 2.1 Alur penguraian kata sandi dengan penyandian siklis di       |

| sisi penerima                                                           |

| Gambar 2.2 Alur penyandian dengan penggabungan 2 teknik secara          |

| serial                                                                  |

| Gambar 2.3 Arsitektur Von Neuman                                        |

| Gambar 2.4 Arsitektur Harvard                                           |

| Gambar 3.1 Model Rangkaian error correction dengan penggabungan         |

| teknik RS (15,5) dan BCH (15,5) pada simulink21                         |

| Gambar 3.2 Pengaturan parameter blok "Sumber Pesan"                     |

| Gambar 3.3 Pengaturan parameter blok <i>Encoder</i> RS (15,5)           |

| Gambar 3.4 Pengaturan parameter blok <i>Encoder</i> BCH (15,5)          |

| Gambar 3.5 Rangkaian subsistem "Channel (penyisipan error)" dengan      |

| pola <i>error</i> mengelompok                                           |

| Gambar 3.6 Pengaturan parameter blok <i>Multiport Selector</i>          |

| Gambar 3.7 Rangkaian subsistem "masukan <i>error</i> "                  |

| Gambar 3.8 Rangkaian subsistem "Channel (penyisipan error)" dengan      |

| pola menyebar                                                           |

| Gambar 3.9 Pengaturan parameter blok saluran AWGN                       |

| Gambar 3.10 Pengaturan parameter blok "Decoder BCH (15,5)               |

| Gambar 3.11 Algoritma penanaman model simulink ke DSK                   |

| TMS320C6713 sebagai embedded target30                                   |

| Gambar 3.12 Model rangkaian error correction dengan penggabungan        |

| teknik RS (15,5 dan BCH (15,5) untuk DSK TMS320C6713 31                 |

| Gambar 3.13 Konfigurasi Parameter Model                                 |

| Gambar 3.14 Proses <i>Diagnostic</i>                                    |

| Gambar 4.2 Model Simulink penyandian RS (7,5) dan BCH (7,4)             |

| Gambar 4.2 Skema pemrosesan 1 <i>frame</i> data dengan penggabungan     |

| RS (15,5) dan BCH (15,5)                                                |

| Gambar 4.3 Ilustrasi penyandian BCH (15,5) dengan panjang masukan 5b 40 |

|                                                                         |

|                                                                         |

|                                                                         |

|                                                                         |

|                                                                         |

|                                                                         |

# **DAFTAR TABEL**

|                                                                                    | Halaman |

|------------------------------------------------------------------------------------|---------|

| Tabel 2.1 Polinomial Primitif Pada GF(2)                                           | 9       |

| Tabel 2.2 Tabel 2.2 Polinomial Minimal dari Elemen-elemen GF(2 <sup>4</sup> ) yang |         |

| dibangkitkan oleh $p(x) = 1 + x + x^4$                                             | 10      |

| Tabel 2.3 Representasi α dari elemen GF(2 <sup>4</sup> ) dibangkitkan oleh         |         |

| $p(x) = 1 + x + x^4$                                                               | 11      |

| Tabel 4.1 Data hasil pengujian Simulink untuk penyandian RS (7,5) dan              |         |

| BCH (7,4)                                                                          |         |

| Tabel 4.2 Karakteristik decoding BCH (15,5) dengan error lebih dari 3 bi           | t       |

| mengelompok di belakang                                                            | 41      |

| Tabel 4.3 Karakteristik decoding BCH (15,5) dengan error lebih dari 3 bi           |         |

| mengelompok di depan                                                               | 42      |

| Tabel 4.4 Karakteristik <i>decoding</i> RS (15,5) dengan <i>error</i> lebih dari   |         |

| 5 simbol mengelompok di belakang                                                   | 42      |

| Tabel 4.5 Hasil pengujian sistem menggunakan simulink dengan <i>error</i>          |         |

| mengelompok sebelum bit ke-65                                                      | 43      |

| Tabel 4.6 Hasil pengujian sistem dengan kesalahan menyebar                         |         |

| menggunakan saluran AWGN                                                           | 45      |

| Tabel 4.7 Tinjauan letak bit error menyebar                                        | 46      |

| Tabel 4.8 Data hasil uji Simulink dengan parameter yang sama dengan                |         |

| uji DSK                                                                            | 50      |

|                                                                                    |         |

# BAB 1 PENDAHULUAN

#### 1.1 LATAR BELAKANG MASALAH

Di tengah perkembangan sistem komunikasi digital yang begitu pesat, kemajuan di bidang teknologi memegang peranan penting. Di antara yang mendorong begitu cepatnya perkembangan teknologi komunikasi digital adalah adanya tuntutan kebutuhan akan suatu sistem perngiriman data digital dan sistem penyimpanan data yang efisien dan handal. Selain itu juga dipercepat oleh mendesaknya kebutuhan akan sistem komunikasi data dengan skala besar dan kecepatan tinggi di berbagai lingkup kehidupan. Namun demikian, semaju apapun teknologi sistem komunikasi digital, tetap ada faktor yang terlibat dalam sistem tersebut yang menyebabkan tidak dapat dicapainya suatu kondisi yang ideal. Faktor tersebut berupa gangguan dalam saluran transmisi atau media penyimpanan data yang menyebabkan informasi yang diterima atau dibaca dari media penyimpanan mengalami perubahan atau kerusakan. Gangguan tersebut dapat berupa derau atau interferensi pada saluran transmisi, dan tidak sempurna atau cacatnya media penyimpanan.

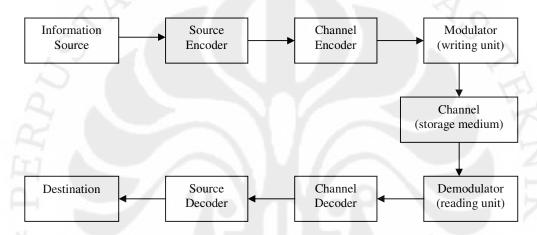

Untuk mempertahankan informasi yang dikirim hingga sampai ke pengguna diperlukan suatu mekanisme yang dapat melindungi informasi tersebut, yang salah satunya adalah dengan menggunakan kata sandi atau penyandian terhadap informasi yang hendak dikirim (*error control codes*). Dengan metode penyandian ini data yang diterima dapat diterjemahkan kembali ke bentuk informasi aslinya meskipun telah mengalami perubahan atau kerusakan karena penyandian ini berfungsi untuk memperbaiki kesalahan yang terjadi pada informasi digital. Gambar 1.1 menujukkan sebuah diagram blok sistem transmisi atau penyimpanan data yang menerapkan teknik penyandian untuk meminimalkan dampak gangguan dalam saluran atau media penyimpanan.

Untuk menghasilkan sebuah *error control codes*, ada beberapa macam teknik penyandian salah satunya yaitu penyandian jenis siklis (*cyclic code*). Penyandian siklis memiliki kelebihan dibandingkan dengan jenis penyandian lainnya di antaranya adalah dapat mendeteksi dan mengoreksi adanya kesalahan

data yang diterima sekaligus. Teknik penyandian yang termasuk dalam jenis siklis dan banyak dikembangkan untuk memperbaiki kemampuannya di dalam mengoreksi kesalahan, di antaranya RS (*Reed-Solomon*), BCH (*Bose Chaudhuri Hocquenhem*), dan Meggit. Penggabungan teknik yang ada memungkinkan untuk melengkapi karakter dan kemampuan masing-masing teknik dalam memperbaiki kesalahan yang lebih bervariasi. Penggunaan program simulink memungkinkan penggabungan kedua teknik yaitu RS dan BCH untuk dirancang dan disimulasikan untuk selanjutnya rancangan tersebut diterapkan pada perangkat DSK TMS320C6713.

Gambar 1.1 Diagram blok sistem transmisi atau penyimpanan data [1]

#### 1.2 PERUMUSAN MASALAH

Berdasarkan latar belakang tersebut, dapat dirumuskan masalah yaitu bagaimana merancang rangkaian sistem *error correction* untuk komunikasi digital dengan penggabungan dua penyadian yang diterapkan pada perangkat DSP. Rumusan masalah dapat diperinci menjadi tiga pertanyaan sebagai berikut:

- 1. Bagaimana penggabungan teknik penyandian BCH dan RS dapat meningkatkan kemampuan memperbaiki kesalahan informasi?

- 2. Bagaimana merancang gebungan teknik penyandian BCH dan RS menggunakan program simulink?

- 3. Bagaimana menerapkan rancangan dari program simulink ke dalam perangkat DSK?

#### 1.3 TUJUAN

Skripsi ini bertujuan untuk merancang bangun rangkaian simulasi yang berfungsi memperbaiki kesalahan dalam komunikasi digital dengan menggabungkan dua teknik penyandian yaitu penyandian RS (15,5) dan penyandian BCH (15,5) melalui program simulink yang diaplikasikan pada perangkat DSK TMS320C6713.

#### 1.4 BATASAN MASALAH

Perancangan perangkat *error correcting* ini menggunakan dua jenis penyandian siklis yaitu penyandian RS (15,5) dan BCH (15,5) secara berurutan dengan pesan awal sepanjang 5 simbol *integer*. Panggabungan kedua teknik penyandian tersebut dilakukan dengan konfigurasi sesial menggunakan program simulink. Hasil perancangan menggunakan program simulink tersebut kemudian diterapkan pada perangkat DSK TMS320C6713, tanpa membahas tentang teknik modulasi yang digunakan dalam simulasi dan pengujian DSK hanya menggunakan fasilitas RTDX untuk memperoleh data dari DSK.

#### 1.5 SISTEMATIKA PENULISAN

Penulisan tugas akhir ini disusun berdasarkan sistematika sebagai berikut.

#### Bab 1 Pendahuluan

Berisi latar belakang masalah, perumusan masalah, tujuan penulisan, batasan masalah, dan sistematika penulisan.

# Bab 2 Penyandian siklis dan DSK TMS320C6713

Berisi tentang prinsip dasar dari penyandian blok siklis secara umum, penyandian BCH dan Reed-Solomon serta DSK TMS320C6713.

#### Bab 3 Perancangan simulasi

Berisi mekanisme perancangan simulasi baik menggunakan simulink maupun perangkat DSK TMS320C6713.

#### Bab 4 Pengujian dan analisis sistem

Berisi pengujian rancangan simulasi sistem *error correction* dengan simulink dan DSK TMS320C6713 serta analisis terhadap sistem.

#### Bab 5 Kesimpulan

Berisikan kesimpulan yang didapat dari tugas akhir ini.

# BAB 2 PENYANDIAN SIKLIS DAN DSK TMS320C6713

#### 2.1 KONSEP PENYANDIAN SIKLIS

Penyandian siklis merupakan salah satu jenis penyandian blok linier. Penyandian ini menggunakan struktur matematika aljabar linier dengan bentuk polinomial pada pembentukan kata sandi dan penguraian kata sandi, sedangkan penyandian lainnya menggunakan matriks dalam pembentukan kata sandi dan penguraiannya sehingga penyandian model siklis lebih mudah dalam melakukan penyandian dan penguraian dibandingkan jenis penyandian blok lainnya. Namun demikian, pembentukan kata sandi pada penyandian siklis juga dapat dilakukan dengan operasi matriks yang merupakan operasi dasar dari pembentukan kata sandi pada penyandian blok.

Suatu penyandian biner dikatakan sebagai penyandian siklis jika memiliki 2 sifat dasar, yaitu [1]:

- 1. Sifat linier, artinya yaitu bila 2 buah kata sandi dijumlahkan maka hasilnya juga merupakan sebuah kata sandi.

- 2. Sifat siklis, artinya pergeseran siklis dari suatu kata sandi adalah kata sandi.

Sifat linier pada penyandian siklis menegaskan bahwa penyandian siklis adalah pernyandian blok linier. Misalkan  $c = (c_0, c_1, c_2, ...., c_{n-1})$  adalah suatu kata sandi dari penyandian blok linier (n,k), jika dilakukan pergeseran siklis maka kata sandi dengan n digit berbentuk  $(c_{n-1}, c_0, c_0, ...., c_{n-2})$ ,  $(c_{n-2}, c_0, c_0, ...., c_{n-1})$ ,  $(c_1, c_2, c_3, ...., c_0)$ . Contoh tersebut menunjukkan sifat siklis yang dimiliki penyandian siklis. Sifat siklis ini juga menandakan bahwa unsur pembentuk kata sandi dengan panjang n dapat dianggap sebagai koefisien dari suatu polinomial dengan pangkat (n-1), sehingga kata sandi dengan unsur pembentuk  $(c_0, c_1, c_2, ...., c_{n-1})$  dapat dinyatakan dalam bentuk polinomial kata sandi berikut [3]:

$$c(x) = (c_0 + c_1 x + \dots + c_{n-1} x^{n-1})$$

(2.1)

dan bila digeser siklis dapat ditulis:

$$c^{(i)}(x) = c_{n-1} + c_{n+1-i}x + \dots + c_{n-1}x^{i-1} + c_0x^i + c_1x^{i+1} + \dots + c_{n-i-1}x^{n-1}$$

(2.2)

dimana:

i = jumlah pergeseran

n = jumlah bit dalam satu blok

c = dapat bernilai 0 atau 1

Jika x  $^{n-1}$  = 1 maka tiap pangkat x dari polinomial c(x) mewakili satu pergeseran siklis, sehingga perkalian polinomial c(x) dengan x dipandang sebagai pergeseran siklis atau satu putaran ke kanan. Bentuk perkalian polinomial ini merupakan modulo  $(x^n - 1)$ , dimana untuk satu pergeseran siklis [2]:

$$xc(x) \operatorname{mod}(x^{n} - 1) = c_{n-1} + c_0 x + \dots + c_{n-2} x^{n-1}$$

(2.3)

# 2.2 POLINOMIAL GENERATOR DAN PARITY CHECK PADA PENYANDIAN SIKLIS

Polinomial generator siklis adalah suatu polinomial yang digunakan dalam perhitungan pembentukan kata sandi dan penguraiannya dengan berdasarkan pada faktor penyandian siklis (n,k) yang dispesifikasikan oleh polinomial kata sandi berderajat (n-1) atau kurang, dan memiliki polinomial berderajat (n-k) sebagai faktornya. Polonomial ini dinyatakan dengan g(x). Derajat g(x) menunjukkan banyaknya bit pariti polonomial generator g(x) ekivalen dengan matriks generator g(x) pada penyandian blok linier.

Polinomial pariti pemeriksa (*parity check*) dibentuk oleh polinomial yang berderajat k dan disebut h(x). Polinomial *parity check* merupakan bentuk ekivalen dari matriks penyandian blok linier sesuai dengan hubungan [2]:

$$h(x)g(x)\operatorname{mod}(x^{n}-1)=0 \tag{2.4}$$

Sesuai dengan sifat dasar siklis bahwa setiap kelipatan polinomial generator g(x) dari pengandian siklis (n,k) adalah polinomial kata sandi, maka dari persamaan (2.4) diperoleh bahwa setiap polinomial kata sandi c(x) memenuhi persamaan [2]:

$$h(x)c(x)\operatorname{mod}(x^{n}-1)=0$$

(2.5)

Polinomial generator dan polinomial *parity check* memiliki sifa-sifat dasar yaitu:

1. Polinomial generator penyandian siklis (n,k) adalah satu-satunya polinomial kata sandi yang berderajat minimum (n-k) dan dapat ditulis:

$$g(x) = g_0 + g_1 x + g_2 x^2 + \dots + g_{n-k-1} x^{n-k-1} + x^{n-k}$$

(2.6)

Dimana  $g_0 = 1$ , agar syarat derajat minimum tercapai.

2. Perkalian polinomial g(x) dengan satu polinomial p(x) adalah polinomial kata sandi juga bila p(x) adalah polinomial dalam x. Sehingga dapat ditulis:

$$c(x) = p(x)g(x) \operatorname{mod}(x^{n} - 1)$$

(2.7)

3. Polinomial generator g(x) dan polinomial *parity check* h(x) adalah faktor dari polinomial (x<sup>n</sup>+1) sesuai dengan persamaan:

$$h(x)g(x) = x^{n} + 1$$

(2.8)

Dimana perhitungan aritmatika modulo-2, nilai  $(x^n + 1)$  sama dengan  $(x^n - 1)$  dan perkalian g(x) dengan p(x) dalam bentuk yang diperluas:

$$p(x)g(x) = p_0g(x) + p_1g(x) + \dots + p_{k-1}x^{k-1}g(x)$$

(2.9)

Dari sifat dasar siklis pertama diketahui  $x^ng(x)$  adalah polinomial kata sandi, oleh sebab itu dapat disimpulkan bahwa setiap perkalian dari g(x) modulo  $(x^n - 1)$  adalah kata sandi juga seperti pada persamaan (2.9). Kesimpulan ini dapat dinyatakan bahwa satu polinomial biner berderajat n-1 atau kurang adalah polinomial kata sandi, jika dan hanya jika polinomial tersebut adalah kelipatan g(x).

Berdasarkan sifat dasar siklis, khususnya sifat ketiga, maka dapat dikatakan bahwa bila g(x) adalah polinomial berderajat (n-k) dan merupakan faktor dari  $x^n$  +1, maka g(x) adalah polinomial generator dari penyandian siklis (n,k). Seperti pada g(x), maka h(x) adalah polinomial *parity check* penyandian siklis (n,k) bila h(x) adalah polinomial berderajat k dan merupakan faktor dari  $x^n$  +1. Hal inilah yang menjadi dasar pemilihan polinomial generator dan polinomial *parity check*.

# 2.3 PROSES PENYANDIAN (ENCODING)

Proses penyandian pada penyandian siklis bertujuan untuk membentuk kata sandi pada sisi pengirim untuk dikirimkan melalui sebuah kanal. Pembentukan kata sandi berdasarkan pada polinomial generator g(x) yang dipilih. Agar didapat penyandian siklis yang sistematis, blok informasi terpisah dari blok pariti dan harus memenuhi struktur berikut[3]:

$$(h_0, h_1, h_2, ..., h_{n-k-1}, m_0, m_1, m_2, ..., m_{k-1})$$

dimana  $h_0$  hingga  $h_{n-k-1}$  adalah bit-bit pariti dan  $m_0$  hingga  $m_{k-1}$  adalah bit-bit informasi.

Jika  $m(x) = m_0 + m_1 x + ... + m_{k-1} x^{k-1}$  adalah polinomial informasi, maka untuk memenuhi struktur sistematis polinomial m(x) dikalikan dengan  $x^{n-k}$ , maka diperoleh:

$$x^{n-k}m(x) = m_0 x^{n-k} + m_1 x^{n-k+1} + \dots + m_{k-1} x^{n-1}$$

(2.10)

Polinomial pariti h(x) adalah sisa pembagian terhadap g(x). Maka persamaan pembentukan kata sandi sistematis adalah:

$$x^{n-k}m(x) = v(x)g(x) + h(x)$$

(2.11)

dimana v(x) adalah hasil pembagian.

Persamaan (2.11) dapat dituliskan kembali menjadi:

$$h(x) + x^{n-k}m(x) = v(x)g(x)$$

(2.12)

Pada persamaan (2.12) polinomialnya merupakan kelipatan dari polinomial generator g(x), maka polinomial itu adalah polinomial kata sandi dari penyandian siklis (n,k) yang dihasilkan oleh g(x). Hal ini dapat ditunjukkan pada persamaan:

$$c(x) = h(x) + x^{n-k} m(x)$$

(2.13)

Maka untuk membentuk kata sandi sistematis, penyandian siklis (n,k) dilakukan tiga tahap, yaitu [1]:

- 1. Polinomial informasi m(x) dikalikan dengan x<sup>n-k</sup>.

- 2. Bagi  $x^{n-k}m(x)$  dengan polinomial generator g(x) untuk menghasilkan sisa h(x).

- 3. Polinomial kata sandi c(x) adalah penambahan h(x) terhadap  $x^{n-k}m(x)$ .

# 2.4 PROSES PENGURAIAN (DECODING)

Proses penguraian kata sandi pada dasarnya melakukan perhitungan sindrom (*syndrome*). Perhitungan sindrom diperlukan untuk memeriksa apakah kata sandi yang diterima mengalami kerusakan atau perubahan ataukah tidak. Misalnya kata sandi  $c=(c_0,c_1,c_2,....,c_{n-1})$  ditransmisikan dan mengalami gangguan sehingga menghasilkan kata sandi yang diterima  $r=(r_0,r_1,r_2,....,r_{n-1})$  dengan polinomial yang diterima r(x). Maka terdapat unsur kesalahan e atau polinomial e(x) pada kata sandi yang diterima r(x), sehingga persamaan polinomial dari kondisi ini [1]:

$$r(x) = c(x) + e(x)$$

(2.14)

Polinomial sindrom s(x) merupakan sisa pembagian r(x) terhadap g(x) dan dapat dituliskan sebagai persamaan:

$$s(x) = r(x) \bmod g(x) = s_0 + s_1 x + \dots + s_{n-k-1} x^{n-k-1}$$

(2.15)

Jika terjadi kesalahan atau timbulnya polinomial e(x) maka  $s(x) \neq 0$ , tetapi jika tidak terjadi kesalahan mana s(x) = 0 dan e(x) = 0. Jika persamaan (2.14) dihubungkan dengan persamaan (2.15), maka e(x) menjadi:

$$e(x) = c(x) + a(x)g(x) + s(x)$$

(2.16)

dimana a(x) adalah hasil bagi r(x) terhadap g(x).

Dari persamaan (2.16) dapat dilihat tujuan penguraian adalah untuk memperkirakan polinomial kesalahan e(x) dari polinomial sindrom.

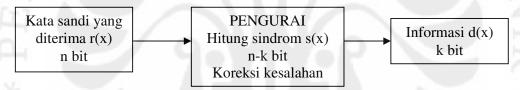

Alur penguraian kata sandi yang diterima pada penyandian siklis dapat dilihat pada Gambar 2.1 berikut:

Gambar 2.1 Alur Penguraian Kata Sandi Dengan Penyandian Siklis di Sisi Penerima

# 2.5 PENYANDIAN DAN PENGURAIAN PADA TEKNIK PENYANDIAN SIKLIS BCH DAN RS

Penyandi (*encoder*) dan pengurai (*decoder*) pada penyandian siklis banyak dikembangkan dengan teknik-teknik khusus yang bertujuan meningkatkan kemampuan memperbaiki kesalahan kata sandi. Panjang informasi yang akan disandikan sangat menentukan tingkat perbaikan kesalahan yang dapat dilakukan oleh teknik penyandian siklis. Dari beberapa teknik penyandian yang ada, terdapat dua teknik yang memiliki keunggulan dalam tingkat perbaikan kesalahannya. Kedua teknik itu adalah Bose Chaudhury Hocquenghem (BCH) dan Reed-Solomon (RS).

### **2.5.1** Bose Chaudhury Hocquenghem (BCH)

Pada tahun 1959 Hocquenghem merepresentasikan suatu metode penyandian siklis yang memiliki tingkat perbaikan kesalahan yang tinggi dengan pembentukan kata sandi yang lebih spesifik. Kemudian pada tahun 1960 metode tersebut disempurnakan oleh Bose dan Chaudhury, sehingga teknik penyandian ini disebut Bose Chaudhury Hocquenghem atau BCH.

#### 2.5.1.1 Polinomial Generator

Perhitungan pada penyandian BCH melibatkan perhitungan aritmatika *Galois Field* (GF), yaitu suatu area dari dua elemen biner yang operasi penjumlahan dan perkaliannya didefinisikan pada modulo-2 dan dinyatakan sebagai GF (2<sup>m</sup>). *Galois Field* sangat berhubungan dengan panjang kata sandi (n), dan dapat dituliskan dengan persamaan:

$$n = 2^m - 1 (2.17)$$

Kemampuan memperbaiki kesalahan pada teknik BCH dinyatakan sebagai t dengan persamaan[1]:

$$t \ge \frac{n-k}{m} \tag{2.18}$$

dimana t menunjukkan jumlah bit yang mampu diperbaiki dalam satu blok.

Jika n = 15 pada BCH (15,5) disubstitusikan ke dalam persamaan (2.17) akan diperoleh nilai m = 4 atau GF ( $2^4$ ). Kemudian nilai-nilai yang ada disubstitusikan ke dalam persamaan (2.18), sehingga dipeoleh  $t \ge \frac{15-5}{4} \approx 3$ , yang berarti kemampuan perbaikan dari BCH (15,5) adalah 3 digit. Untuk penyandian dengan GF ( $2^4$ ) dibangkitkan polinomial primitif  $p(x) = 1 + x + x^4$ , dimana p(x) adalah polinomial primitif untuk GF( $2^4$ ) yang tidak dapat difaktorkan lagi. Tabel 2.1 menunjukkan polinomial primitif untuk GF( $2^m$ ) dari nilai m = 2 sampai dengan m = 27.

Tabel 2.1 Polinomial Primitif Pada GF(2)[1]

| m | p(x)          | m  | p(x)                            |

|---|---------------|----|---------------------------------|

| 2 | $x^2 + x + 1$ | 15 | $x^{15} + x + 1$                |

| 3 | $x^3 + x + 1$ | 16 | $x^{16} + x^{12} + x^3 + x + 1$ |

| 4 | $x^4 + x + 1$ | 17 | $x^{17} + x^3 + 1$              |

| 5  | $x^5 + x^2 + 1$                 | 18 | $x^{18} + x^7 + 1$           |

|----|---------------------------------|----|------------------------------|

| 6  | $x^6 + x + 1$                   | 19 | $x^{19} + x^5 + x^2 + x + 1$ |

| 7  | $x^7 + x^2 + 1$                 | 20 | $x^{20} + x^3 + 1$           |

| 8  | $x^8 + x^4 + x^3 + x^2 + 1$     | 21 | $x^{21} + x^2 + 1$           |

| 9  | $x^9 + x^4 + 1$                 | 22 | $x^{22} + x + 1$             |

| 10 | $x^{10} + x^3 + 1$              | 23 | $x^{23} + x^5 + 1$           |

| 11 | $x^{11} + x^2 + 1$              | 24 | $x^{24} + x^7 + x^2 + x + 1$ |

| 12 | $x^{12} + x^6 + x^4 + x + 1$    | 25 | $x^{25} + x^3 + 1$           |

| 13 | $x^{13} + x^4 + x^3 + x + 1$    | 26 | $x^{26} + x^6 + x^2 + x + 1$ |

| 14 | $x^{14} + x^{10} + x^6 + x + 1$ | 27 | $x^{27} + x^5 + x^2 + x + 1$ |

Polinomial generator untuk tingkat kemampuan perbaikan t pada BCH adalah polinomial berderajat rendah dari GF(2) yang memiliki  $(\alpha, \alpha^2, \alpha^3, ..., \alpha^{2t})$  untuk  $g(\alpha^i) = 0$  setiap akar-akarnya, dimana nilai untuk  $1 \le i \le 2t$ . Polinomial g(x) dibentuk berdasarkan polinomial minimal g(x). Polinomial minimal g(x) ditentukan untuk setiap g(x) yang memiliki koefisien dan akar-akarnya saling berkonjugasi. Maka polinomial generator dengan tingkat kemampuan perbaikan t dibentuk dari gabungan perkalian terkecil LCM (*Least Common Multiple*) dari  $\phi_1(x), \phi_2(x), ..., \phi_{2t}(x)$ , dan dinyatakan dengan [1]:

$$g(x) = LCM\{\phi_1(x), \phi_2(x), ..., \phi_{2t}(x)\}$$

(2.19)

Tabel 2.2 Polinomial Minimal dari Elemen-elemen GF(2<sup>4</sup>) yang dibangkitkan oleh

$$p(x) = 1 + x + x^4 [3]$$

| Polinomial minimal        |  |  |

|---------------------------|--|--|

| x                         |  |  |

| 1+ x                      |  |  |

| $1 + x + x^4$             |  |  |

| $1 + x + x^2 + x^3 + x^4$ |  |  |

| $1 + x + x^2$             |  |  |

| $1+x^3+x^4$               |  |  |

|                           |  |  |

Dengan menggunakan tabel 2.2 di atas maka persamaan (2.19) dapat disederhanakan menjadi persamaan [1]:

$$g(x) = LCM\{\phi_1(x), \phi_3(x), ..., \phi_{2t-1}(x)\}$$

(2.20)

Dari persamaan (2.18) dan persamaan (2.20) dapat dibentuk polinomial generator untuk BCH (15,5) dengan t = 3, yaitu:

$$g(x) = LCM \{ \phi_1(x), \phi_3(x), \phi_5(x) \}$$

$$g(x) = (1+x+x^4)(1+x+x^2+x^3+x^4)(1+x+x^2)$$

$$g(x) = 1+x+x^2+x^4+x^5+x^8+x^{10}$$

Derajat polinomial tertinggi dari generator yang dihasilkan dari persamaan (2.20) adalah 10. Hasil ini sesuai dengan teori untuk membentuk kata sandi dengan n = 15 dan panjang informasi k = 5 diperlukan derajat polinomial tertinggi dari generator tersebut adalah:

$$|\deg(g(x))| = 15 - 5 = 10$$

Untuk melakukan penyandian dibentuk suatu konstruksi dari perhitungan aritmatika dengan suatu nilai  $\alpha$  yang mewakili posisi biner dari kombilasi biner  $2^3$  seperti diberikan pada Tabel 2.3.

Tabel 2.3 Representasi  $\alpha$  dari elemen GF(2<sup>4</sup>) dibangkitkan oleh  $p(x) = 1 + x + x^4$  [3]

| Representasi<br>Eksponen                    | Representasi<br>Polinomial         | Representasi vektor |   |   |   |

|---------------------------------------------|------------------------------------|---------------------|---|---|---|

| 0                                           | 0                                  | 0                   | 0 | 0 | 0 |

| 1                                           | /_1/                               | 1                   | 0 | 0 | 0 |

| $\alpha$                                    | α                                  | 0                   | 1 | 0 | 0 |

| $\alpha^2$                                  | $\alpha^2$                         | 0                   | 0 | 1 | 0 |

| $\alpha^3$                                  | $\alpha^3$                         | 0                   | 0 | 0 | 1 |

| $lpha^4$                                    | $1+\alpha$                         | 1                   | 1 | 0 | 0 |

| $\alpha^5$                                  | $\alpha + \alpha^2$                | 0                   | 1 | 1 | 0 |

| $\alpha^6$                                  | $\alpha^2 + \alpha^3$              | 0                   | 0 | 1 | 1 |

| $\alpha^7$                                  | $1+\alpha+\alpha^3$                | 1                   | 1 | 0 | 1 |

| $\alpha^8$                                  | $1+\alpha^2$                       | 1                   | 0 | 1 | 0 |

| $\alpha^9$                                  | $\alpha + \alpha^3$                | 0                   | 1 | 0 | 1 |

| $\alpha^{\scriptscriptstyle 10}$            | $1+\alpha+\alpha^2$                | 1                   | 1 | 1 | 0 |

| $\alpha^{11}$                               | $\alpha + \alpha^2 + \alpha^3$     | 0                   | 1 | 1 | 1 |

| $\boldsymbol{lpha}^{\scriptscriptstyle 12}$ | $1 + \alpha + \alpha^2 + \alpha^3$ | 1                   | 1 | 1 | 1 |

| $\alpha^{13}$                               | $1+\alpha^2+\alpha^3$              | 1                   | 0 | 1 | 1 |

| $oldsymbol{lpha}^{14}$                      | $1+\alpha^3$                       | 1                   | 0 | 0 | 1 |

### 2.5.1.2 Penyandian

Proses pembentukan kata sandi pada teknik yang digunakan dalam penyandian siklis bergantung dari aturan-aturan yang digunakan dalam masingmasing teknik. Pada BCH, proses pembentukan kata sandi mengikuti prinsip dasar proses pembentukan kata sandi pada penyandian siklis.

Jika pada BCH (15,5) panjang kata sandi n = 15, panjang informasi k = 5, dan  $g(x) = 1 + x + x^2 + x^4 + x^5 + x^8 + x^{10}$ , maka dapat dibentuk kata sandi dengan menggunakan persamaan (2.11) dan (2.13):

$$h(x) + x^{n-k}m(x) = v(x)g(x)$$

$$c(x) = h(x) + x^{n-k} m(x)$$

dimana:

- m(x) adalah polinomial informasi,

- g(x) adalah polinomial generator,

- v(x) adalah polinomial hasil pembagian  $x^{n-k}d(x)$  terhadap g(x),

- h(x) adalah polinomial sisa pembagian, dan

- c(x) adalah polinomial kata sandi.

### 2.5.1.3 Penguraian

#### Perhitungan Sindrom

Jika kata sandi yang diterima merupakan kata sandi yang ditambah dengan polinomial kesalahan e(x), maka sindrom akan dihitung dari polinomial kata sandi yang diterima r(x). Pada BCH dengan tingkat kemampuan perbaikan t, banyaknya sindrom q ditentukan melalui persamaan sebagai berikut[1]:

$$q = 2t \tag{2.21}$$

Masing-masing terdiri dari 2 bit. Untuk BCH (15,5) dengan t = 3, jumlah sindrom q = 6 atau  $(S_1, S_2, S_3, S_4, S_5, S_6)$ . Sehingga perhitungan sindrom dapat dilakukan sebagai berikut [2]:

$$Si = r(\alpha^{i})$$

$$= r_{0} + r_{1}\alpha^{i} + r_{2}\alpha^{2i} + ... + r_{14}\alpha^{14i}$$

(2.22)

karena polinomial r(x) dibentuk oleh polinomial minimal  $\phi_i(x)$  dari  $\alpha^i$ , maka:

$$r(x) = \alpha_i(x)\phi_i(x) + b_i(x) \tag{2.23}$$

koefisien  $b_i(x)$  menyatakan sisa dengan derajat yang tidak kurang dari  $\phi_i(x)$  dan karena  $\phi_i(x) = 0$ , maka diperoleh[1]:

$$Si = r(\alpha^{i}) = b_{i}(\alpha^{i}) \tag{2.24}$$

Dari sindrom yang diperoleh, pengurai akan mencari polinomial pola kesalahan e(x) untuk menentukan letak kesalahan yang terdapat pada suatu kata sandi r(x) dengan jangkauan dari  $\mathbf{x}^0$  sampai  $\mathbf{x}^{n-1}$ . Karena  $\alpha, \alpha^2, \alpha^3, ..., \alpha^{2t}$  adalah akar-akar dari polinomial kata sandi, dimana  $c_i(x) = 0$  untuk  $1 \le i \le 2t$ , sehingga dapat dinyatakan hubungan sindrom dan pola kesalahan:

$$Si = e(\alpha^i) \tag{2.25}$$

Dimana pola kesalahan e(x) memiliki w kesalahan pada lokasi  $x^{j1}, x^{j2}, ..., x^{jw}$  membentuk  $e(x) = x^{j1}, x^{j2}, ..., x^{jw}$  dan  $S_{2i} = (\alpha^{j1})^{2i}, (\alpha^{j2})^{2i}, ..., (\alpha^{jw})^{2i}$  dengan nilai-nilai  $\alpha^{j1}, \alpha^{j2}, ..., \alpha^{jw}$  sebagai koefisien-koefisien  $\alpha$  yang menyatakan posisi biner yang tidak diketahui.

Pada BCH (15,7) dengan kemampuan perbaikan t = 3 atau kurang, sindrom yang akan dihitung adalah  $S_1$  sampai dengan  $S_6$  dan dapat dituliskan[1]:

$$S_{1} = \mathbf{r}(\alpha) = e_{j_{1}}\beta_{1} + e_{j_{2}}\beta_{2} + \dots + e_{j_{\nu}}\beta_{\nu}$$

$$S_{2} = \mathbf{r}(\alpha^{2}) = e_{j_{1}}\beta_{1}^{2} + e_{j_{2}}\beta_{2}^{2} + \dots + e_{j_{\nu}}\beta_{\nu}^{2}$$

$$\vdots$$

$$S_{2t} = \mathbf{r}(\alpha^{2t}) = e_{j_{1}}\beta_{1}^{2t} + e_{j_{2}}\beta_{2}^{2t} + \dots + e_{j_{\nu}}\beta_{\nu}^{2t}$$

(2.26)

dimana v adalah jumlah lokasi kesalahan.

Penentuan Polinomial Pola Kesalahan (e(x))

Teknik penentuan lokasi kesalahan pada BCH dengan kondisi [4]:

1. untuk 1 kesalahan

$$\tau = S_1$$

2. untuk 2 kesalahan

$$\tau_1 = S_1$$

$$\tau_2 = \frac{S_3 + S_1^3}{S_1}$$

3. untuk 3 kesalahan

$$\tau_{1} = S_{1}$$

$$\tau_{2} = \frac{S_{1}^{2} S_{3} + S_{5}}{S_{3} + S_{1}^{3}}$$

$$\tau_{3} = S_{3} + S_{1}^{3} + S_{1}\tau_{2}$$

## 2.5.2 Reed-Solomon (RS)

Pada Desember 1958 Irving S. Reed dan Gustavo Solomon menyelesaikan laporan berjudul "polunomial codes over certain finite fields" pada M.I.T. Lincoln Laboratory. Kemudian tahun 1960 dilakukan sedikit modifikasi pada laporan tersebut dan diumumkan pada sebuah jurnal Society for Industrial and Applied Mathematics (SIAM) dan dikenal sebagai Reed-Solomon Codes yang merupakan sandi terbaru dalam perbaikan kesalahan.

Penyadian RS yang sekarang digunakan sebagai sistem koreksi kesalahan, banyak dijumpai untuk berbagai keperluan, di antaranya [5]:

- 1. Media penyimpanan data (*Storage devices*), seperti *hard disk*, *compact disk* (CD), DVD, dan *barcode*

- 2. Komunikasi nirkabel, seperti telepon bergerak dan microwave links

- 3. Televisi digital

- 4. Komunikasi satelit, termasuk untuk misi ruang angkasa

- 5. Broadband modems (ADSL, xDSL).

Penyandian RS dengan menyisipkan sandi tambahan ke dalam data aslinya. Data yang telah disandikan bisa jadi disimpan dalam media penyimpanan atau ditransmisikan. Saat data tersebut dibaca kembali atau diterima, kemungkinan telah mengalami kerusakan, misalnya karena goresan pada CD, permukaan *hard disk* yang tidak sempurna, atau interferensi frekuensi radio pada telepon bergerak. Sandi tambahan tersebut memungkinkan pengurai untuk mendeteksi bagian mana dari data yang mengalami kerusakan atau berubah dan kemudian memperbaikinya.

#### 2.5.2.1 Polinomial Generator

Perhitungan pada Reed-Solomon juga menggunakan perhitungan aritmatika *finite field* dari elemen q yang dinotasikan dengan GF(q) dimana jumlah dari

elemen dalam sebuah *finite field* dibentuk dari  $q = 2^m$ . Reed-Solomon dengan simbol dari GF(q) memiliki parameter-parameter sebagai berikut[2]:

Panjang sandi blok : n = q-1Jumlah digit *parity check* : n - k = 2tJarak minimum :  $d_{min} = 2t + 1$

$$n = 2^m - 1 (2.27)$$

Maka untuk generator polinomial dari sebuah polinomial primitif dengan panjang blok  $2^m$  -1 adalah:

$$g(x) = (x + \alpha)(x + \alpha^{2})...(x + \alpha^{2t})$$

$$= g_{0} + g_{1}x + ... + g_{2t}x^{2t-1} + x^{2t}$$

dimana g(x) memiliki  $\alpha, \alpha^2, ..., \alpha^{2t}$  sebagai akar-akar dan koefisien dari  $GF(2^m)$ .

## 2.5.2.2 Penyandian

Proses pembentukan kata sandi dengan Reed-Solomon sama dengan pembentukan kata sandi dengan BCH.

Misalkan,  $a(x)=a+a_1x+a_2x^2...+a_{k-1}x^{k-1}$  adalah informasi yang akan dibentuk kata sandinya dan k = n - 2t. Dalam kata sandi dengan bentuk sistematis, digit dari *parity check* (2t) adalah koefisien dari sisa pembagian  $h(x)=h_0+h_1x+h_2x^2...+h_{2t-1}x^{2t-1}$  yang dihasilkan dari pembagian polinomial informasi  $x^{2t}a(x)$  terhadap polinomial g(x).

# 2.5.2.3 Penguraian

Dalam proses penguraian kata sandi dengan teknik Reed-Solomon diperlukan tiga tahapan yang juga terdapat pada proses penguraian kata sandi dengan BCH, dengan tambahan satu tahapan yaitu perhitungan dari nilai kesalahan. Komponen sindrom 2t didapat dengan menggantikan  $\alpha^i$  ke dalam polinomial kata sandi yang diterima r(x) untuk i = 1, 2, ..., 2t. Sehingga:

$$S_1 = r(\alpha)$$

$$S_2 = r(\alpha^2)$$

$$S_{2i} = r(\alpha^{2i})$$

(2.28)

Komponen sindrom Si dapat juga dihitung dengan membagi r(x) dengan  $x + \alpha^i$ .

$$r(x) = c_i(x)(x + \alpha^i) + b_i$$

(2.29)

Dimana sisa pembagian  $b_i$  adalah sebuah konstanta dalam GF(2<sup>m</sup>). Substitusikan  $\alpha^i$  ke dalam persamaan (2.29), maka diperoleh:

$$S_i = b_i$$

Untuk mencari polinomial dari lokasi kesalahan:

$$\tau(x) = (1 + \beta_1 x)(1 + \beta_2 x)...(1 + \beta_v x)$$

= 1 + \tau\_1 x + ... + \tau\_v x

dimana  $\beta_l = \alpha^{jl}$  untuk l = 1, 2, ..., v adalah sebagai jumlah lokasi kesalahan.

## 2.5.3 Penggabungan Reed-Solomon (15,5) Dengan BCH (15,5)

Penyandian siklis banyak diimplementasikan pada perangkat keras sehingga teknik-teknik penyandian dan penguraian yang dikembangkan tidak dapat digabungkan karena masing-masing memiliki perangkat keras yang berbeda. Namun jika teknik-teknik ini diimplementasikan pada perangkat DSP prosesor yang menggunakan program simulink untuk rekayasa penggabungannya, maka kendala terhadap perbedaan karakter yang ditemui pada perangkat keras yang terpisah tidak terjadi lagi.

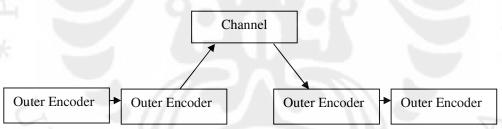

Penggabungan teknik penyandian RS (15,5) dan BCH (15,5) dilakukan secara serial (*concatenated*). Alasan penggabungan kedua teknik secara serial adalah sebagai berikut:

- Kemudahan dalam melakukan penyandian maupun dalam penguraian. Hal ini disebabkan kecocokan dimensi antara keluaran dari blok penyandi RS (15,5) dan masukan untuk blok penyandi BCH (15,5).

- Perhitungan yang lebih sederhana jika dibandingkan menggunakan nilai n yang lebih besar.

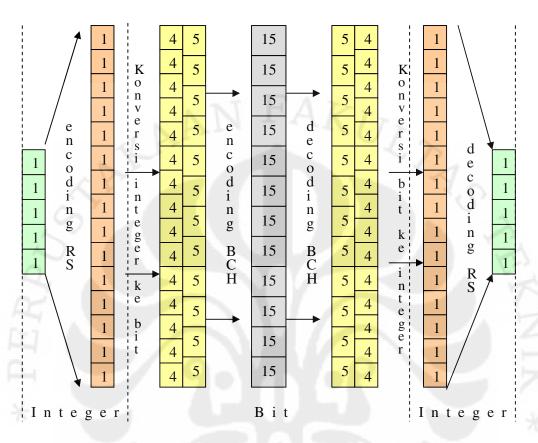

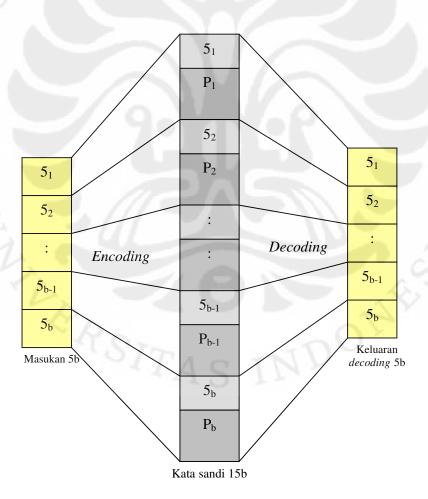

Pada penggabungan secara serial, proses penyandian akan dilakukan dua tahap dimana tahap pertama yaitu informasi sepanjang 20 bit dengan 4 bit per simbolnya yang akan dikirim disandikan terlebih dahulu dengan teknik RS (15,5). 15 simbol keluaran penyandi RS direpresentasikan oleh 4 bit sehingga panjang kata sandinya menjadi 60 bit. Kemudian pada tahap kedua kata sandi dari RS (15,5) disandikan lagi dengan teknik BCH (15,5) sehingga menghasilkan panjang

kata sandi 180 *bit*. Penyandi dengan teknik RS (15,5) dalam hal ini disebut sebagai *outer encoder* sedangkan penyandi dengan teknik BCH (15,5) disebut sebagai *inner encoder*.

Proses penguraiannya juga melalui dua tahap dimana tahap pertama kata sandi yang diterima diuraikan dengan teknik BCH (15,5). Setelah itu pada tahap kedua kata sandi yang telah diuraikan dengan teknik BCH (15,5) diuraikan lagi dengan teknik RS (15,5). Pengurai BCH (15,5) dalam hal ini disebut sebagai *inner decoder* sedangkan pengurai RS (15,5) disebut sebagai *outer decoder*.

Penggabungan secara serial ini juga efektif untuk mengatasi kesalahan secara acak maupun secara berurutan dimana pola dari *byte* yang tidak dapat dikoreksi dengan *inner code* harus dikorekasi dengan *outer code*. Kesalahan secara acak dapat dikorekasi oleh *inner code* dan untuk beberapa kesalahan secara berurutan yang kemungkinan tidak dapat dikoreksi oleh *inner code* akan dikoreksi oleh *outer code*. Gambar 2.2 menunjukkan tahapan proses *encoding* hingga *decoding*.

Gambar 2.2 Alur Penyandian Dengan Penggabungan 2 Teknik Secara Serial

# 2.6 DIGITAL SIGNAL PROCESSING STARTER KIT (DSK) TMS320C6713[6]

Digital Signal Processing Starter Kit (DSK) TMS320C6713 adalah salah satu DSP tipe C6000 yang dapat bekerja pada fixed-point maupun floating- point. Akan tetapi DSP ini masih berupa starter kit, yaitu suatu platform yang dapat mensimulasikan DSP C6713 yang sebenarnya. DSK ini lebih ditujukan untuk keperluan edukasi, penelitian, serta evaluasi. Namun hasil dari aplikasi yang dibuat di DSK ini sangat mungkin untuk diterapkan pada DSP C6713 yang sebenarnya.

#### 2.6.1 Digital Signal Processing Starter Kit (DSK) Prosesor

Prosesor yang digunakan oleh DSK adalah prosesor yang khusus dibuat untuk memproses sinyal secara digital. Prosesor yang digunakan sebagai DSP berbeda dengan mikroprosesor pada umumnya (*general purpose microprocessor*). DSP mempunyai sifat-sifat serta karakteristik yang unik bila dibandingkan dengan mikroprosesor biasa, seperti:

# a. Operasi Matematika

Sebuah prosesor DSP dapat melakukan operasi matematika jauh lebih cepat bila dibandingkan dengan mikroprosesor biasa. Hal ini disebabkan karena DSP memiliki unit-unit aritmatika, logika, dan *discrete multiplier* yang lebih banyak. Unit-unit tersebut didesain untuk bekerja dengan kecepatan tinggi sehingga berbagai opersi matematika dapat dilakukan hanya dalam satu *cycle* dari *clock*. Sehingga DSP mampu melakukan opersi *multiple-accumulate* yang banyak digunakan dalam pemrosesan sinyal *digital*.

# b. Pemakaian memori yang hemat

Pemrograman DSP tidak memerlukan memori internal yang besar. Hal ini disebabkan karena dengan kecepatannya yang tinggi, DSP dapat menggunakan memori dengan lebih efisien. Prosesor DSP yang paling modern saat ini hanya mempunyai memori sekitar 8 k*byte* sampai 256 k*byte*.

### c. Pengolahan data kontinu

DSP dapat diaplikasikan pada proses pengolahan yang datanya terus mengalir secara kontinu (*stream*).

# d. Konsumsi daya yang rendah

Mikroprosesor biasa memerlukan daya yang relatif besar. Contohnya dapat dilihat pada *Personal Computer* (PC). Mikroprosesor PC mengkonsumsi daya sekitar 10 sampai 100 watt. Dengan konsumsi daya sebesar ini, jika diaplikasikan pada alat yang menggunakan baterai AA, maka umur baterai mungkin hanya sampai 11 menit. Sedangkan prosesor DSP hanya mengonsumsi daya sekitar 100 miliwatt. Dengan konsumsi daya seperti ini, baterai AA dapat dipakai hingga 18 jam.

#### e. Real-time

DSP dapat melakukan pemrosesan sinyal secara *real-time*. Hal ini disebabkan

karena DSP dapat mengolah aliran data yang datang secara serus menerus. *Real-time* juga dapat diartikan tidak adanya jeda waktu (*delay*) antara *input* dan *output*, sehingga saat data dimasukkan ke sebuah sistem, saat itu juga data diproses dan keluar dari sistem.

#### 2.6.2 Arsitektur DSP Prosesor

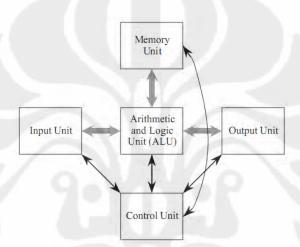

Pada dasarnya DSP juga sebuah mikroprosesor, sehingga memiliki arsitektur tertentu. Secara umum, terdapat dua macam arsitektur komputer yang sudah banyak dikenal yaitu Von Neuman dan Harvard.

#### a. Von Neuman

Gambar 2.3 Arsitektur Von Neuman [6]

Pada arsitektur Von Neuman seperti pada Gambar 2.3 terdapat 2 unit operasi dasar, yaitu *Arithmatic and Loogical Unit* (ALU) dan *Input/Output* (I/O). ALU berfungsi untuk melakukan operasi aritmatika dan logika, sedangkan I/O berfungsi untuk mengaturkeluar masuknya data. Ciri arsitektur ini adalah program dan data disimpan pada memori yang sama.

#### b. Harvard

Unit operasi dasar yang digunakan sama dengan arsitektur Von Neuman. Perbedaannya terletak pada alokasi memorinya. Dapat dilihat pada Gambar 2.4 bahwa pada arsitektur Harvard, alokasi memori untuk program dan data berada pada lokasi yang terpisah. Oleh karena itu, pada arsitektur ini instruksi dan data dapat ditransfer secara bersamaan sehingga meninggatkan kecepatan proses.

Gambar 2.4 Arsitektur Harvard [6]

Dari kedua arsitektur di atas, arsitektur yang banyak digunakan untuk prosesor DSP adalah arsitektur Harvard. Hal ini dikarenakan aplikasi DSP memerlukan kecepatan proses yang tinggi agar dapat memproses sinyal secara *real-time*. Namun pemisahan lokasi memori program dan data menyebabkan perlunya tambahan pin-pin serta memori yang digunakan. Sehingga harga prosesor DSP di pasaran menjadi lebih tingi dari prosesor biasa.

### 2.6.3 Starting DSK TMS320C6713

Pada saat DSK board dinyalakan, DSP prosesor akan mulai untuk melakukan loading code berdasarkan boot mode yang sudah ditentukan dari pabrik. Power On Self Test (POST) yang telah diprogram dalam flash dan jumper akan melakukan boot dari flash memori. POST akan terus melakukan looping sampai Code Composer Studio (CCS) diaktifkan. Embedded USB controller akan mulai aktif dan menunggu koneksi dari software CCS. Saat software DSK 6713 dibuka, secara otomatis software akan melakukan koneksi ke USB port dan bila koneksi sudah tercipta, software DSK 6713 CCS akan melakukan loading dan kemudian dapat digunakan oleh user. Saat melakukan koneksi dari software keUSB pada DSK board, akan muncul Windows Hardware Device Manager. Kemudian pada saat CCS dimulai, driver emulation akan melakukan kontak ke DSK board. Lalu CCS akan melakukan proses download emulation formware dari DSK. Setelah selesai, firmware akan memutuskan koneksi USB dan melakukan koneksi ulang sebagai emulator. Setelah kita keluar dari program CCS dan mengulang kembali proses menyalakan program, program akan otomatis melakukan koneksi melalui USB host ke DSK sebagai emulator dan bila DSKberada dalamkondisi menyala, program baru dapat diluncurkan. USB controller tidak dipengaruhi oleh tombol reset pada board DSK. Saat DSK menyala, USB *controller* mendapatkan daya saat *reset*.

# BAB 3 PERANCANGAN SIMULASI

#### 3.1 SIMULINK

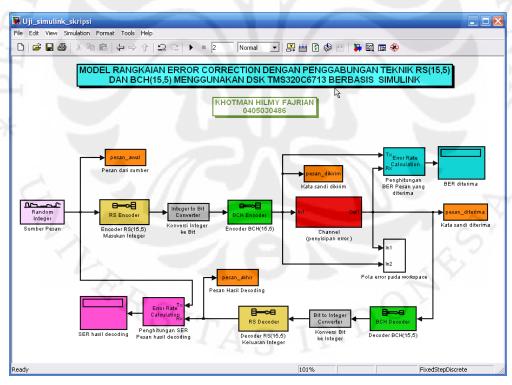

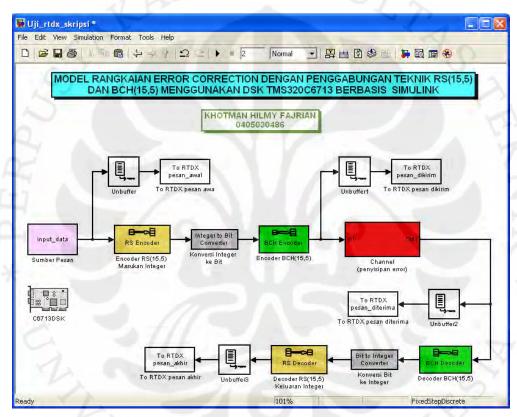

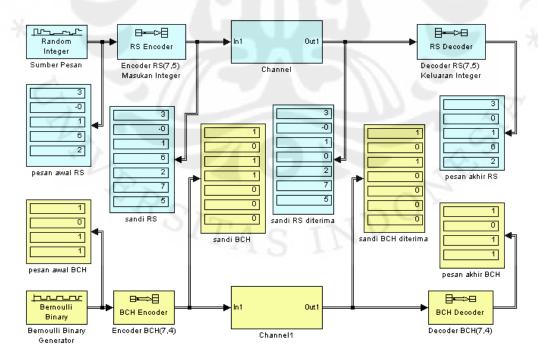

Simulink merupakan sebuah perangkat lunak sub-program dari MATLAB yang dirancang untuk digunakan dalam pembuatan model dari suatu sistem terutama di bidang teknik, termasuk di dalamnya sistem pemrosesan sinyal, serta mensimulasikannya sesuai dengan parameter-parameter yang ditentukan. Model sistem dibuat dengan cara merangkai blok-blok yang terdapat di dalam Simulink *library* sesuai dengan fungsi blok yang dikehendaki. Model rangkaian *error correction* dengan penggabungan teknik penyandian Reed-Solomon (15,5) dan BCH (15,5) dibangun dengan merangkaikan blok-blok fungsi yang diperlukan untuk sistem tersebut, sebagaimana dapat dilihat pada Gambar 3.1.

**Gambar 3.1** Model Rangkaian *error correction* dengan penggabungan teknik RS (15,5) dan BCH (15,5) pada simulink

Penjelasan tiap blok dari model rangkaian *error correction* pada Gambar 3.1 diuraikan selanjutnya.

#### 3.1.1 Blok "Sumber Pesan"

Blok "Sumber Pesan" adalah sebuah blok yang berfungsi untuk membangkitkan suatu sinyal sebagai pesan atau informasi yang selanjutnya akan disandikan. Blok pembangkit sinyal yang digunakan sebagai sumber adalah blok *Random Integer Generator* yang membangkitkan sinyal berupa bilangan bulat positif berbasis 10 (desimal) secara acak. Parameter dari blok ini disesuaikan dengan karakteristik data masukan dari blok penyandi RS (15,5) yang akan dilalui oleh data tersebut selanjutnya. Tampilan pengaturan parameter blok sumber ini diperlihatkan pada Gambar 3.2.

Gambar 3.2 Pengaturan parameter blok "Sumber Pesan"

Parameter 'M-ary number' diberikan nilai 16 yang berarti sinyal yang akan dibangkitkan adalah 16 bilangan pertama dari bilangan cacah, yaitu dari 0 sampai dengan 15. Nilai 16 ini adalah nilai maksimum yang dapat diberikan agar data yang dibangkitkan sesuai dengan karakter blok *encoder* RS (15,5) masukan *integer* yang masukannya harus berupa bilangan bulat positif antara 0 sampai dengan n, dalam hal ini n sama dengan 15. Selanjutnya data yang dibangkitkan dipilih berbetuk *frame-based data* dengan 5 sampel per *frame*-nya sebab blok *encoder* RS (15,5) mempunyai syarat masukannya harus berbentuk *frame-based*

dengan jumlah k sampel per *frame*. Sehingga dengan nilai parameter *sample time* sama dengan 1/5 maka blok ini akan membangkitkan 1 *frame* data yang berisi 5 sampel dengan nilai bulat antara 0 sampai 15 secara acak tiap satu periodenya.

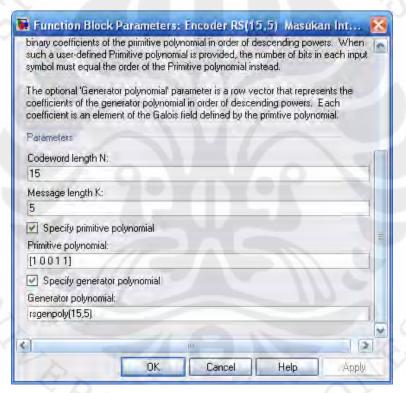

# 3.1.2 Blok "Encoder RS (15,5) Masukan Integer"

Blok "Encoder RS (15,5) Masukan Integer" adalah sebuah blok penyandi Reed-Solomon dengan masukan berupa bilangan bulat positif berbentuk frame-based data. Parameter yang ditentukan pada blok ini adalah nilai n dan k serta dapat juga ditentukan polonomial primitifnya dalam bentuk matriks koefisien. Pengaturan parameter blok Encoder RS (15,5) ini dapat dilihat pada Gambar 3.3 berikut.

Gambar 3.3 Pengaturan parameter blok Encoder RS (15,5)

Nilai 15 pada parameter *Codeword length N* menunjukkan bahwa blok ini akan menghasilkan kata sandi dengan panjang 15 simbol atau kelipatan bulat positifnya. Sedangkan parameter *Message length K* diisikan nilai 5 berarti masukan blok ini berupa data berbentuk *frame* dengan panjang 5 simbol atau kelipatan bulat positifnya. Simbol pada masukan dan keluaran dari blok ini haruslah berupa bilangan bulat yang dapat direpresentasikan oleh 4 digit biner,

yaitu bilangan desimal mulai dari 0 sampai 15. Parameter *Primitive polynomial* diisi dengan vektor baris yang berisi koefisien dari polinomial primitif yang digunakan. Vektor [1 0 0 1 1] mewakili bentuk polinomial berderajat 4  $p(x) = 1 + x + x^4$ . Parameter ini boleh juga tidak ditentukan dengan menghilangkan tanda *check* pada *Specify primitive polynomial*. Jika tidak ditentukan nilainya, program simulink sendiri yang mencari nilainya berdasarkan nilai N dan K yang telah ditentukan.

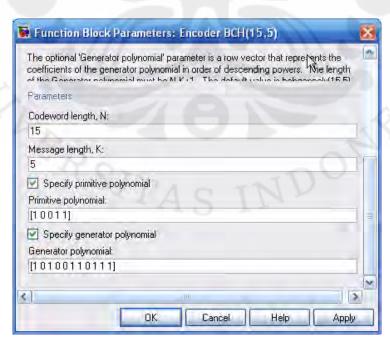

# 3.1.3 Blok "Encoder BCH (15,5)"

Blok "Encoder BCH (15,5)" adalah sebuah blok penyandi dengan teknik BCH primitif, yaitu penyandian BCH yang masukannya berupa data biner. Parameter yang harus ditentukan pada blok ini antara lain panjang pesan atau masukan K dan panjang kata sandi N. Nilai yang dimasukkan untuk panjang kata sandi N adalah 15 dan untuk panjang pesan K adalah 5. Sedangkan parameter Primitive polynomial dan Generator polynomial dapat dituliskan sendiri atau bisa juga tidak, namun hanya ada satu nilai yang sesuai. Dalam skripsi ini penulis menentukan sendiri polinomial primitif dan generatornya. Pengaturan parameter blok Encoder BCH (15,5) dapat dilihat pada Gambar 3.4.

Gambar 3.4 Pengaturan parameter blok *Encoder* BCH (15,5)

Pada Gambar 3.4, nilai [1 0 0 1 1] untuk parameter *primitive polynomial* mewakili polinomial  $p(x) = 1 + x + x^4$  dan nilai [1 0 1 0 0 1 1 0 1 1 1] untuk parameter *generator polynomial* mewakili polonomial  $g(x) = 1 + x + x^2 + x^4 + x^5 + x^8 + x^{10}$ . Sebelum masuk ke blok *Encoder* BCH (15,5), data yang masih berbentuk *integer* dikonversi terlebih dahulu ke bentuk biner menggunakan blok "Konversi *Integer* ke *Bit*". Blok konversi ini mengubah tiap nilai *integer* yang masuk ke dalam susunan 4 digit biner atau *bit*. Jumlah 4 *bit* ini disesuaikan dengan masukannya yang mempunyai rentang nilai dari 0 sampai dengan 15.

## 3.1.4 Blok "Channel (Penyisipan Error)"

Blok "Channel (Penyisipan Error) adalah suatu blok subsistem yang berfungsi sebagai penambah kesalahan pada data, yang mewakili saluran transmisi atau media penyimpanan. Dalam uji simulasi yang akan diuraikan pada bab 4, blok ini dibagi menjadi 2 jenis dengan fungsi yang sama namun memberikan pola kesalahan yang berbeda. Kedua pola kesalahan itu adalah pola kesalahan mengelompok dan pola kesalahan menyebar. Penerapan kedua pola kesalahan tersebut ke dalam sistem bertujuan untuk menguji keandalan sistem dalam mengoreksi kesalahan yang mungkin terjadi dengan pola bervariasi. Untuk menghasilkan pola kesalahan mengelompok, blok subsistem "channel" ini dibangun dengan rangkaian blok seperti pada Gambar 3.5.

Gambar 3.5 Rangkaian subsistem "Channel (penyisipan error)" dengan pola error mengelompok

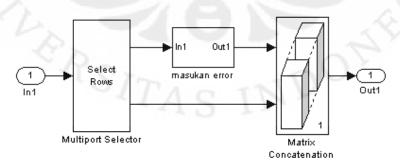

Pada Gambar 3.5, blok "Multiport Selector" berfungsi untuk memilih elemen ke berapa dari sebuah frame data yang akan disisipkan dengan error.

Pemilihan elemen yang akan disisipkan *error* dilakukan dengan cara menentukan parameter pembagian data *frame* yang masuk melalui kotak dialog seperti pada Gambar 3.6. Isian pada parameter '*Indices to output*' menujukkan bahwa tiap *frame* data yang masuk akan dibagi menjadi 2 keluaran dimana keluaran pertama berisi elemen baris ke-1 sampai elemen ke-60 dari data *frame* tersebut. Sedangkan keluaran kedua berisi elemen baris ke-61 sampai elemen ke-180.

Gambar 3.6 Pengaturan parameter blok Multiport Selector

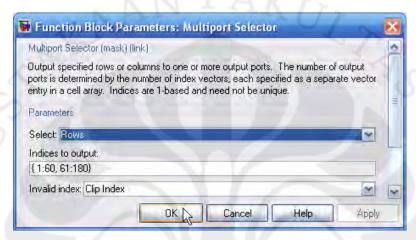

Selain blok *Multiport Selector*, dalam subsistem *channel* juga terdapat subsistem "masukan *error*" yang berfungsi menghasilkan *error* terhadap data yang masuk dengan mengubah nilai data biner 0 menjadi 1 dan 1 menjadi 0. Pengubahan nilai *bit* tersebut dilakukan dengan menambahkannya dengan 1 menggunakan operator logika "XOR", seperti terlihat pada gambar 3.7.

Gambar 3.7 Rangkaian subsistem "masukan error"

Sedangkan blok "*Matrix Concatenation*" berfungsi menyusun kembali data yang telah terbagi menjadi data yang mengalami *error* dan data yang tidak mengalami *error* ke dalam 1 *frame* dengan urutan elemen yang tidak berubah.

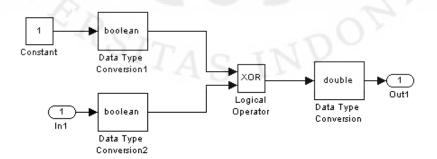

Sedangkan untuk menghasilkan pola kesalahan yang menyebar, subsistem "*channel*" dibangun dengan rangkaian blok seperti pada Gambar 3.8.

Gambar 3.8 Rangkaian subsistem "Channel (penyisipan error)" dengan pola menyebar

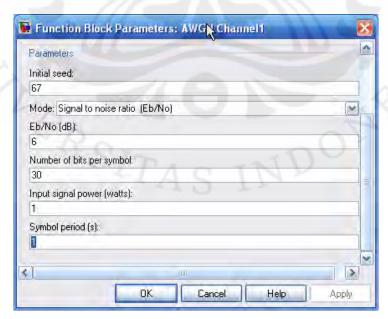

Rangkaian ini menggunakan modulasi dan demodulasi dengan tipe BPSK (Binary Phase Shift Keying) dan dilewatkan pada saluran AWGN (Additive White Gaussian Noise). Blok saluran AWGN ini yang berfungsi menambahkan kesalahan pada data secara acak atau menyebar. Parameter yang ada pada blok saluran AWGN di atur sedemikian sehingga menyebabkan kesalahan dengan probabilitas yang dikehendaki. Parameter blok saluran AWGN dapat dilihat pada Gambar 3.9.

Gambar 3.9 Pengaturan parameter blok saluran AWGN

Untuk parameter Eb/No(dB) dan *number of bits per symbol*, menambahkan nilainya akan menurunkan probabilitas *error* yang ditimbulkan dan mengurangkannya akan menaikkan probabilitas *error*.

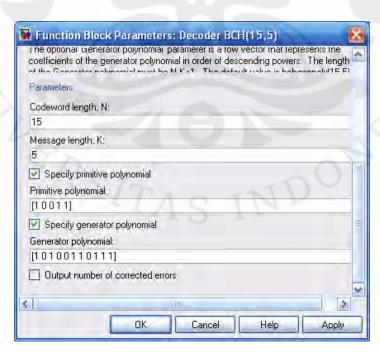

#### 3.1.5 Blok "Decoder BCH (15,5)"

Blok "Decoder BCH (15,5)" merupakan pasangan dari blok "Encoder BCH (15,5)" dan berfungsi untuk mendeteksi serta mengoreksi kesalahan yang dialami oleh data selama dalam saluran transmisi. Kemampuannya dalam mengoreksi kesalahan tergantung pada nilai parameter Codeword length N dan Message length K yang diberikan. Berdasarkan persamaan (2.18) dengan nilai n=15 dan n=5 berarti encoder BCH (15,5) mampu mengoreksi 3 bit error pada tiap 15 bit kata sandi. Blok ini menerima data masukan frame sepanjang 180 bit dan menghasilkan keluaran dengan panjang 60 bit. Data biner ini kemudian diubah ke integer menggunakan blok "Konversi Bit ke Integer", dimana tiap 4 bit dikonversi menjadi sebuah simbol berupa bilangan integer bernilai 0 hingga 15. Sehingga panjang data 60 bit dikonversi menjadi 15 simbol integer. Pengubahan ini diperlukan untuk proses decoding selanjutnya oleh decoder RS. Gambar 3.10 memperlihatkan parameter-parameter untuk blok decoder BCH (15,5).

Gambar 3.10 Pengaturan parameter blok "Decoder BCH (15,5)

## 3.1.6 Blok "Decoder RS (15,5) Keluaran Integer"

Blok "Decoder RS (15,5) Keluaran Integer" adalah pasangan dari blok "Encoder RS (15,5) Masukan Integer" dan berfungsi untuk mendeteksi serta mengoreksi kesalahan yang dialami oleh data selama berada dalam saluran transmisi. Kemampuannya dalam mengoreksi kesalahan juga tergantung pada nilai N dan K yang diberikan sebagaimana blok encoder BCH. Berdasarkan persamaan n – k = 2t, dengan nilai n =N=15 dan k=K=5 menunjukkan bahwa decoder RS (15,5) mampu mengoreksi maksimum 5 simbol error. Masukan blok ini adalah data frame sepanjang 15 simbol integer, yaitu keluaran blok decoder BCH yang telah dikonversi dari bit ke integer. Sedangkan keluarannya adalah data frame sepanjang 5 simbol integer dan merupakan hasil akhir dari sistem error correction yang dirancang. Idealnya hasil akhir ini diharapkan sama dengan data awal yang dibangkitkan oleh blok "Random Integer".

#### 3.1.7 Blok "Perhitungan BER" dan "Perhitungan SER"

Blok "Perhitungan BER" berfungsi melakukan perhitungan BER (*Bit Error* Rate) atau laju terjadinya kesalahan *bit* dengan cara membandingkan jumlah *bit error* yang masuk terhadap jumlah keseluruhan *bit* yang masuk. Data yang dihitung BER-nya adalah data yang diterima dibandingkan dengan data yang dikirim. Tujuan penghitungan BER ini adalah untuk mengetahui tingkat kesalahan yang ditimbulkan oleh saluran yang digunakan dalam proses transmisi.

Blok "Perhitungan SER" berfungsi melakukan perhitungan SER (*Symbol Error Rate*) atau laju terjadinya kesalahan simbol pada pesan akhir hasil keseluruhan proses *decoding*. Perhitungannya dilakukan dengan membandingkan jumlah simbol yang mengalami kesalahan dari data atau pesan akhir terhadap jumlah seluruh simbol yang telah diproses dari pesan awal yang dibangkitkan oleh *interger generator*. Tujuan penghitungan SER ini adalah untuk mengetahui keandalan sistem *error correction* yang dibuat dalam menanggulangi kedua pola kesalahan yang mungkin terjadi. Dengan membandingkan nilai SER terhadap nilai BER, dapat diketahui secara kasar seberapa besar sistem tersebut dapat mereduksi kesalahan yang terjadi dalam saluran transmisi atau media penyimpanan.

#### 3.2 PENERAPAN MODEL SIMULINK KE DSK TMS320C6713

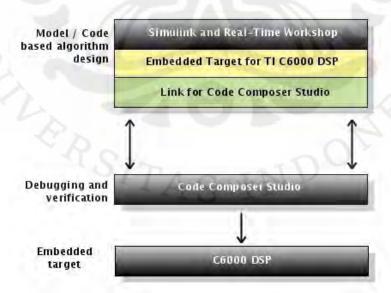

Model rangkaian error correction yang telah dibuat pada simulink dapat kemudian dimasukkan dalam DSK TMS320C6713 dengan hanya melakukan beberapa setting pada Configuration Parameters. Proses debugging dari SIMULINK® ke DSK memerlukan perangkat lunak lain yaitu Code Composer Studio (CCS) yang merupakan sebuah komposer bahasa C/C++ yang digunakan untuk memrogram papan DSK dengan menggunakan bahasa C/C++. Maka sebenarnya yang dilakukan oleh SIMULINK® adalah membangun kode pemrograman dalam bahasa C/C++ dari model yang disimulasikan. Kode pemrograman tersebut kemudian dijalankan oleh CCS. Dan kemudian SIMULINK® dan papan DSK TMS320C6713 dapat berkomunikasi melalui kodekode pemrograman yang dibuat oleh SIMULINK<sup>®</sup>. Inilah kemudahan yang diberikan oleh SIMULINK<sup>®</sup>, yaitu kita tidak perlu membuat dan membangun kode pemrograman dari model yang kita simulasikan. Kita hanya cukup membangun blok model pada SIMULINK® dan dengan mudah kita akan mendapatkan kode pemrograman dalam bahasa C/C++ yang dapat digunakan untuk membuat rancang bangun dari model yang telah kita buat dalam SIMULINK® pada DSK TMS320C6713. Gambar 3.11 menunjukkan algoritma dari penerapan SIMULINK pada DSK.

**Gambar 3.11** Algoritma penanaman model simulink ke DSK TMS320C6713 sebagai *embedded* target [7]

Perancangan simulasi rangkaian *error correction* dengan penggabungan teknik RS (15,5) dan BCH (15,5) pada DSK TMS320C6713 dilakukan tetap menggunakan model simulink yang telah dibuat dengan beberapa perubahan yaitu pada blok sumber dan blok pengambil data *to workspace* serta penambahan blok *target preference* C6713DSK yang tersedia pada *library* simulink. Gambar 3.12 menunjukkan perubahan model rangkaian simulink menjadi model yang akan diterapkan pada DSK.

Gambar 3.12 Model rangkaian *error correction* dengan penggabungan teknik RS (15,5 dan BCH (15,5) untuk DSK TMS320C6713

Pada Gambar 3.12 terlihat bahwa blok "Sumber Pesan" yang semula menggunakan blok "random integer" diganti dengan blok "from workspace" dengan nama variabel "input\_data". Penggunaan blok ini bertujuan agar dapat ditentukan sendiri pesan yang akan diproses saat pengujian menggunakan DSK TMS320C6713. Kemudian, blok to workspace yang semula digunakan untuk mengambil data dari blok yang diinginkan ke dala workspace Matlab diganti dengan blok "To RTDX". RTDX adalah suatu fasilitas yang disediakan oleh

Texas Instrument untuk melakukan pertukaran data antara target dan host. Target dalam hal ini adalah DSK TMS320C6713, sedangkan host adalah prorgam Matlab yang ada di PC atau laptop. Blok "To RTDX" yang disediakan simulink berfungsi untuk mengambil data dari DSK yang terhubung ke blok tersebut. Sedangkan untuk mengamati keluaran dari papan DSK menggunakan oscilloscp, blok DAC perlu ditambahkan ke bagian yang ingin diamati sebagai keluaran.

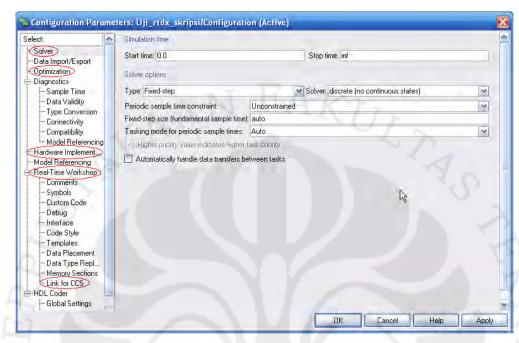

Selain itu juga dibutuhkan Real Time Workshop, Embeded Target for TI (Texas Instrumen) C6000 DSP, dan Link for CCS untuk menghubungkan simulink dengan DSK. Komponen-komponen yang diperlukan tersebut ditemukan pada simulink dan harus dilakukan pengaturan konfigurasi parameter. Pengaturan konfigurasi parameter model rangkaian error correction untuk ketiga hal tersebut dailakukan dengan memilih menu simulation yang ada pada toolbar kemudian pilih konfigurasi parameter. Kotak dialog konfigurasi parameter terlihat pada Gambar 3.13. Pengaturan yang perlu dilakukan antara lain [6]:

- 1. Pada *tab solver*, mengubah *type* menjadi *fixed* dan *solver* menjadi *discrete*.

- 2. Pada *tab optimization*, melakukan *uncheck block reduction* dan *implement logic signal as boolean data* yang terdapat pada menu *simulation and code generation*.

- 3. Pada *tab hardware implementation*, mengubah *device type* yang terdapat pada menu *embeded hardware* menjadi TI C6000.

- 4. Pada *tab real time workshop* di menu *target selection*, mengubah *system target file* menjadi ccslink\_ert.tlc.

- 5. Pada *tab real time workshop subtab debug*, melakukan *check verbose build* pada menu *build process*.

- 6. Pada *tab real time workshop subtab Link for CCS* di menu *project option*, mengubah *system stack size* menjadi 8192.

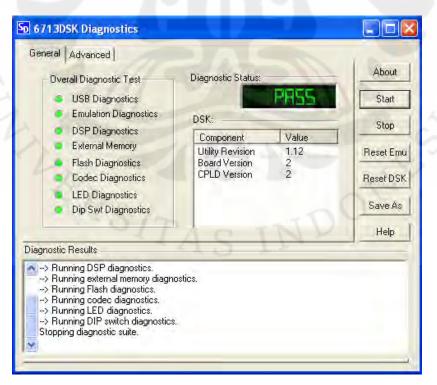

Setelah model rangkaian *error correction* disesuaikan, pemeriksaan koneksi perangkat DSK ke komputer harus dilakukan. DSK harus terhubung ke komputer menggunakan kabel USB dan untuk memastikan keduanya terhubung dengan benar maka proses diagnosa perlu dilakukan. Caranya adalah dengan menggunakan program 6713 *diagnostic* yang disediakan oleh CCS. Jika DSK

terhubung dengan baik ke komputer, maka di kotak dialog program *diagnostic* tersebut akan muncul pesan 'PASS' seperti pada Gambar 3.14.

Gambar 3.13 Konfigurasi Parameter Model

Gambar 3.14 Proses Diagnostic

Kemudian dilakukan proses Incremental Building yang dapat dilakukan dengan memilih menu yang terdapat di tools lalu real time workshop kemudian pilih build model. Setelah dilakukan proses build model, maka matlab akan membuat kode program dalam bahasa C sebagai pengganti blok simulink untuk dijalankan di DSK.

## BAB 4 PENGUJIAN DAN ANALISIS SISTEM

Pengujian terhadap model rangkaian *error correction* dilakukan dengan dua metode, yaitu pengujian simulasi menggunakan simulink dan pengujian dengan perangkat DSK TMS320C6713. Kedua metode pengujian tersebut menggunakan media komputer sebagai penampil akhirnya. Parameter yang akan dilihat dari pengujian adalah nilai kesalahan atau *bit error rate* (BER) dari data yang diterima terhadap data yang dikirim serta data akhir hasil *decoding* terhadap data yang dibangkitkan oleh blok sumber.

# 4.1 PERBANDINGAN HASIL UJI SIMULINK TERHADAP HASIL PERHITUNGAN MANUAL

Untuk membandingkan hasil uji penyandian menggunakan Simulink terhadap hasil perhitungan secara manual berdasarkan teori, maka diambil data hasil pemrosesan sinyal menggunakan teknik penyandian RS (7,5) dan BCH (7,4) secara terpisah menggunakan model Simulink seperti pada Gambar 4.1.

Gambar 4.1 Model Simulink penyandian RS (7,5) dan BCH (7,4)

Pemilihan parameter tersebut hanya untuk mendapatkan proses yang paling sederhana untuk perhitungan secara manual. Hasil pengujian menggunakan Simulink untuk kedua penyandian tersebut dapat dilihat pada Tabel 4.1. Tujuan pembandingan ini adalah untuk membuktikan apakah proses penyandian oleh Simulink sesuai dengan teori.

**Tabel 4.1** Data hasil pengujian Simulink untuk penyandian RS (7,5) dan BCH (7,4)

| Teknik<br>Penyandian | Pesan       | Kata Sandi      | Kata Sandi dengan<br>Kesalahan | Hasil<br>Decoding |

|----------------------|-------------|-----------------|--------------------------------|-------------------|

| RS                   | [2 6 1 0 3] | [5726103]       | [5720103]                      | [2 6 1 0 3]       |

| BCH                  | [1 1 0 1]   | [0 0 0 1 1 0 1] | [0 0 0 0 1 0 1]                | [1 1 0 1]         |

Kemudian dilakukan perhitungan secara manual menggunakan persamaanpersamaan yang terdapat dalam teori penyandian RS (7,5) dan BCH (7,4) dengan operasi aritmatik terhadap koefisien  $\alpha$  mengacu pada tabel elemen GF ( $2^3$ ) yang terdapat pada lampiran. Perhitungannya diuraikan sebagai berikut.

#### 4.1.1 Penyandian RS

- Pesan  $\mathbf{m} = [2\ 6\ 1\ 0\ 3] = [010\ 110\ 001\ 000\ 011]$

- Polinomial pesan  $m(x) = \alpha + \alpha^3 x + \alpha^2 x^2 + \alpha^4 x^4$

- Polinomial generator  $g(x) = (x + \alpha)(x + \alpha^2) = \alpha^3 + \alpha^4 x + x^2$

$$- x^{n-k}m(x) = x^{7-5}(\alpha + \alpha^3 x + \alpha^2 x^2 + \alpha^4 x^4) = \alpha x^2 + \alpha^3 x^3 + \alpha^2 x^4 + \alpha^4 x^6$$

$$- \frac{x^{n-k}m(x)}{g(x)} = v(x) + \frac{h(x)}{g(x)} \Rightarrow$$

$$\frac{\alpha x^{2} + \alpha^{3} x^{3} + \alpha^{2} x^{4} + \alpha^{4} x^{6}}{\alpha^{3} + \alpha^{4} x + x^{2}} = \alpha^{3} + \alpha x + \alpha x^{2} + \alpha x^{3} + \alpha^{4} x^{4} + \frac{\alpha^{6} + \alpha^{5} x}{\alpha^{3} + \alpha^{4} x + x^{2}}$$

- Polinomial pariti  $h(x) = \alpha^6 + \alpha^5 x$

- Polinomial kata sandi

$$c(x) = h(x) + x^{n-k} m(x) = \alpha^6 + \alpha^5 x + \alpha x^2 + \alpha^3 x^3 + \alpha^2 x^4 + \alpha^4 x^6$$

$$\Rightarrow \mathbf{c} = [101\ 111\ 010\ 110\ 001\ 000\ 011] = [5\ 7\ 2\ 6\ 1\ 0\ 3]$$

- Kata sandi yang diterima  $\mathbf{r} = [5 \ 7 \ 2 \ 0 \ 1 \ 0 \ 3] = [101 \ 111 \ 010 \ 000 \ 001 \ 000 \ 011]$

⇒

$$r(x) = c(x) + e(x) = \alpha^6 + \alpha^5 x + \alpha x^2 + \alpha^2 x^4 + \alpha^4 x^6$$

- Sindrom

$$S_i = r(\alpha^i)$$

$\rightarrow$   $S_1 = \alpha^6 + \alpha^6 + \alpha^3 + \alpha^6 + \alpha^{10} = \alpha^6$

$$S_1 = \alpha^6 + \alpha^7 + \alpha^5 + \alpha^{10} + \alpha^9 = \alpha^2$$

- Letak kesalahan  $\sigma \rightarrow [S_1][\sigma] = [S_2] \rightarrow [\sigma] = [S_1]^{-1}[S_2]$

$$\Rightarrow \qquad [\sigma] = [\alpha^6]^{-1}[\alpha^2] = \frac{1}{\alpha^6} \alpha^2 = \frac{\alpha^7}{\alpha^6} \alpha^2 = \alpha^3$$

Sehingga kesalahan terletak pada posisi  $\alpha^3$

- Nilai kesalahan  $e \rightarrow [\sigma][e] = [S_1] \rightarrow [e] = [\sigma]^{-1}[S_1]$

$$\Rightarrow [e] = [\alpha^3]^{-1}[\alpha^6] = \frac{1}{\alpha^3} \alpha^6 = \frac{\alpha^7}{\alpha^3} \alpha^6 = \alpha^{10} = \alpha^3$$

Kesalahan bernilai  $\alpha^3$  di posisi  $\alpha^3$ , sehingga

$$e(x) = \alpha^3 x^3$$