# UNIVERSITAS INDONESIA

# SIMULASI DAN OPTIMISASI DARI SECOND-ORDER DELTA SIGMA MODULATOR DENGAN RESOLUSI EFEKTIF 15 BIT

# **SKRIPSI**

# HANDY CHANDRA 0706267755

# DEPARTEMEN TEKNIK ELEKTRO FAKULTAS TEKNIK UNIVERSITAS INDONESIA JULI, 2011

# UNIVERSITAS INDONESIA

# SIMULASI DAN OPTIMISASI DARI SECOND-ORDER DELTA SIGMA MODULATOR DENGAN RESOLUSI EFEKTIF 15 BIT

# **SKRIPSI**

Diajukan sebagai salah satu syarat untuk memperoleh gelar sarjana

# **HANDY CHANDRA 0706267755**

# DEPARTEMEN TEKNIK ELEKTRO FAKULTAS TEKNIK UNIVERSITAS INDONESIA JULI, 2011

## HALAMAN PERNYATAAN ORISINALITAS

Skripsi ini adalah hasil karya saya sendiri, dan semua sumber baik yang dikutip maupun dirujuk . telah saya nyatakan dengan benar.

Nama : Handy Chandra

NPM : 0706267755

Tanda Tangan : Man

Tanggal : 4 Juli 2011

### **HALAMAN PENGESAHAN**

Skripsi ini diajukan oleh :

Nama : Handy Chandra NPM : 0706267755

Program Studi : Teknik Elektro

Judul : Simulasi dan Optimasi dari Second-Order Delta Sigma

Modulator dengan Resolusi Efektif 15 bit

Telah berhasil dipertahankan di hadapan Dewan Penguji dan diterima sebagai bagian persyaratan yang diperlukan untuk memperoleh gelar Sarjana Teknik pada Program Studi Teknik Elektro, Fakultas Teknik, Universitas Indonesia

# **DEWAN PENGUJI**

Pembimbing : Dr. Ir. Agus Santoso Tamsir, MT.

Penguji 1 : Prof. Dr. Ir. Djoko Hartanto, M.Sc.

Penguji 2 : Prof. Dr. Ir. Harry Sudibyo, M.Sc.

Ditetapkan di : Depok

Tanggal : 4 Juli 2011

## UCAPAN TERIMA KASIH

Pertama – tama saya ingin mengucapkan puji dan syukur kepada Tuhan, karena berkat karunianya saya dapat menyelesaikan skripsi ini. Penulisan skripsi ini dilakukan dalam rangka memenuhi salah satu syarat untuk memperoleh gelar sarjana. Saya menyadari bahwa skripsi ini bisa selesai karena bantuan dan dukungan dari berbagai pihak. Oleh karena itu saya ingin mengucapkan terima kasih kepada:

- 1. Dr. Ir. Agus Santoso Tamsir MT, selaku dosen pembimbing yang telah banyak membimbing dan mengarahkan saya sehingga skripsi ini dapat selesai.

- 2. Teman teman research group CMOS dan MEMS yaitu Nyssa Adi, Renold Partogi, Yediael Christian Hutahaean dan Sandi T.W.

- 3. Keluarga saya yang berada di Padang dan kakak saya yang berada di Jerman, yang sudah memberikan dukungan.

- 4. Teman teman Teknik Elektro 2007, khususnya anak anak lab elektronika yang sudah memberikan dukungan.

Semoga Tuhan membalas segala kebaikan semua pihak yang telah membantu. Semoga skripsi ini membawa manfaat bagi pengembangan ilmu.

Depok, 4 Juli 2011

Penulis

# HALAMAN PERNYATAAN PERSETUJUAN PUBLIKASI TUGAS AKHIR UNTUK KEPENTINGAN AKADEMIS

Sebagai sivitas akademik Universitas Indonesia, saya yang bertanda tangan dibawah ini :

Nama : Handy Chandra

NPM : 0706267755

Program Studi : Teknik Elektro

Departemen : Teknik Elektro

Fakultas : Teknik Jenis Karya : Skripsi

demi pengembangan ilmu pengetahuan, menyetujui untuk memberikan kepada Universitas Indonesia Hak Bebas Royalti Noneksklusif (Non-exclusive Royalti Free Right) atas karya ilmiah saya yang berjudul:

# SIMULASI DAN OPTIMASI DARI SECOND-ORDER DELTA SIGMA MODULATOR DENGAN RESOLUSI EFEKTIF 15 BIT

beserta perangkat yang ada (jika diperlukan). Dengan Hak Bebas Royalti Noneksklusif ini Universitas Indonesia berhak menyimpan, mengalihmedia/formatkan, mengelola dalam bentuk pangkalan data (database), merawat, dan mempublikasikan tugas akhir saya selama tetap mencantumkan nama saya sebagai penulis/pencipta dan sebagai pemilik hak cipta Demikian pernyataan ini saya buat dengan sebenarnya,

Dibuat di : Depok

Pada tanggal : 4 Juli 2011

Yang menyatakan

Handy Chandra

vi

#### **ABSTRAK**

Nama : Handy Chandra Program Studi : Teknik Elektro

Judul : Simulasi dan Optimisasi dari Second-Order Delta-Sigma

Modulator dengan Resolusi Efektif 15 bit

Delta Sigma ADC (Analog to Digital Converter) adalah salah satu jenis ADC dengan resolusi yang lebih tinggi dibandingkan jenis ADC lainnya. Komponen paling penting dari Delta Sigma ADC adalah Delta Sigma Modulator. Terdapat dua faktor yang mempengaruhi resolusi dari Delta Sigma Modulator yaitu oversampling ratio dan topologi rangkaian. Skripsi ini akan membahas simulasi dan optimasi dari salah satu topologi rangkaian Delta Sigma Modulator yaitu Second-Order Delta Sigma Modulator untuk mencapai resolusi yang lebih tinggi. Rangkaian Second-Order Delta Sigma Modulator akan dioptimasi dengan menggunakan topologi fully differential dan dengan menaikkan oversampling ratio agar mencapai resolusi yang lebih tinggi. Kemudian layout integrated circuit dari rangkaian second-order Delta Sigma Modulator akan dibuat dan disimulasikan untuk melihat performa dari rangkaian. Pada simulasi awal didapatkan resolusi modulator sebesar 8 bit. Kemudian optimasi lebih jauh dilakukan dengan mengubah – ubah nilai kapasitor dan kapasitansi parasitik pada modulator untuk melihat pengaruhnya terhadap resolusi dari modulator. Dari hasil percobaan optimasi didapatkan dengan mengubah kapasitor C1,C2 menjadi 0,2 pf dan kapasitansi parasitik poly1 ke substrat dari kapasitor C1,C2 menjadi 1 ff, resolusi modulator naik menjadi 15 bit.

#### Kata kunci:

Second-order Delta Sigma Modulator, Resolusi, Oversampling ratio, Layout integrated circuit

#### **ABSTRACT**

Name : Handy Chandra Study Program : Teknik Elektro

Title : Simulation and Optimization of Second-Order Delta Sigma

Modulator with 15 bit Effective Resolution

Delta Sigma ADC (Analog to Digital Converter) is one of ADC with high resolution. The most important component of Delta Sigma ADC is Delta Sigma Modulator. There are two factors that influence the resolution of Delta Sigma Modulator, which is oversampling ratio and circuit topology. This thesis discusses about simulation and optimization of one topology of Delta Sigma Modulator called Second-Order Delta Sigma Modulator to reach better resolution. Second-Order Delta Sigma circuit will be optimized using fully differential topology and increasing oversampling ratio. Then, integrated circuit layout of Second-Order Delta Sigma Modulator will be made and simulated to look at the performance of the circuit. Simulation reveal that modulator's resolution is 8 bit. Further optimization will be done by changing the value of capacitor and parasitic capacitance to see it's relation to the resolution of the modulator. After optimization is done, better resolution is achieved with the value of C1,C2 0.2 pf and parasitic capacitance poly1 to substrate from C1,C2 is 1 ff. The new effective resolution achieved is 15 bit.

Keywords:

Second-order Delta Sigma Modulator, Resolution, Oversampling ratio, Integrated circuit layout

# **DAFTAR ISI**

| ii   |

|------|

| iii  |

| iv   |

| V    |

| vi   |

| vii  |

| viii |

| ix   |

| xi   |

| xiii |

|      |

| 1    |

| 1    |

| 2    |

| 2    |

| 3    |

|      |

| 4    |

| 4    |

| 5    |

| 5    |

| 7    |

| 8    |

| 8    |

| 9    |

| 11   |

|      |

| 13   |

| 15   |

|      |

| 3.2 Second-order Delta-Sigma Modulator | 18 |

|----------------------------------------|----|

| BAB 4 SIMULASI                         | 21 |

| 4.1 Rangkaian                          |    |

| 4.2 Layout                             | 29 |

| 4.3 Hasil simulasi                     | 39 |

| 4.4 Optimasi                           | 44 |

| BAB 5 KESIMPULAN                       | 49 |

| DAFTAR REFERENSI                       | 51 |

| DAFTAR PUSTAKA                         | 52 |

# **DAFTAR GAMBAR**

| Gambar 2.1  | Proses Kuantisasi                                              | 4    |

|-------------|----------------------------------------------------------------|------|

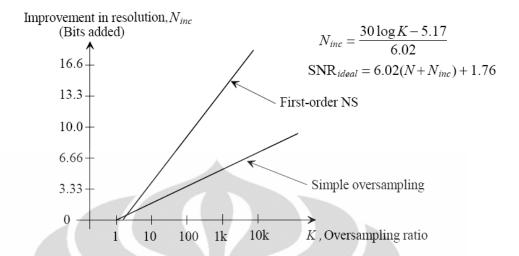

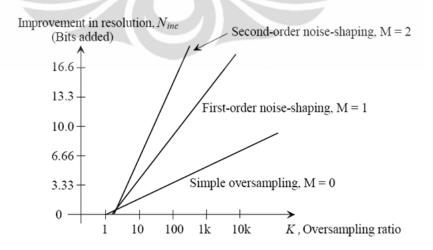

| Gambar 2.2  | Kurva Hubungan oversampling ratio dengan resolusi              | 7    |

| Gambar 2.3  | Tampilan program LTSpice                                       | 9    |

| Gambar 2.4  | Tampilan program Electric VLSI                                 | . 11 |

| Gambar 2.5  | Tampilan program Winspice                                      | . 12 |

| Gambar 3.1  | Delta Sigma Modulator                                          | . 14 |

| Gambar 3.2  | Blok diagram first-order modulator                             | . 15 |

| Gambar 3.3  | Implementasi first-order modulator                             | . 16 |

| Gambar 3.4  | Kenaikan resolusi terhadap oversampling ratio pada first-order |      |

|             | modulator                                                      | . 17 |

| Gambar 3.5  | Model linear first-order modulator                             | . 17 |

| Gambar 3.6  | Second-order modulator                                         |      |

| Gambar 3.7  | Implementasi second-order modulator                            | . 19 |

| Gambar 3.8  | Kenaikan resolusi terhadap oversampling ratio pada second-orer |      |

|             | modulator                                                      | . 19 |

| Gambar 3.9  | Model linear second-order modulator                            | . 20 |

| Gambar 4.1  | Rangkaian simulasi second-order modulator.                     | . 22 |

| Gambar 4.2  | Nonoverlapping clock                                           | . 23 |

| Gambar 4.3  | Transmission gate                                              | . 24 |

| Gambar 4.4  | Switched capacitor                                             | . 25 |

| Gambar 4.5  | Rangkaian Beta Multiplier (BMR)                                | . 25 |

| Gambar 4.6  | Rangkaian Biasing                                              | . 26 |

| Gambar 4.7  | Differential amplifier                                         | . 26 |

| Gambar 4.8  | Output buffer                                                  | . 27 |

| Gambar 4.9  | Switched capacitor CMFB                                        | . 27 |

| Gambar 4.10 | Rangkaian fully differential op-amp                            | . 28 |

| Gambar 4.11 | Rangkaian komparator                                           | . 28 |

| Gambar 4.12 | Layer p-well                                                   | . 30 |

| Gambar 4.13 | Layer n-well                                                   | 30   |

|-------------|----------------------------------------------------------------|------|

| Gambar 4.14 | Layer active                                                   | 30   |

| Gambar 4.15 | Layer p-select                                                 | . 31 |

| Gambar 4.16 | Layer n-select                                                 | 31   |

| Gambar 4.17 | Layer polysilicon1                                             | 31   |

| Gambar 4.18 | Layer polysilicon2                                             | 31   |

| Gambar 4.19 | Layer metal 1 – 5                                              | . 32 |

|             | Layer via                                                      |      |

| Gambar 4.21 | Frame standar untuk layout                                     | . 33 |

| Gambar 4.22 | Layout n-well resistor                                         | 33   |

| Gambar 4.23 | Layout poly1-poly2 kapasitor                                   | . 34 |

| Gambar 4.24 | Layout transmission gate                                       | 35   |

| Gambar 4.25 | Layout beta-multiplier                                         | 36   |

| Gambar 4.26 | Layout rangkaian bias                                          | 36   |

| Gambar 4.27 | Layout differential amplifier                                  | . 37 |

| Gambar 4.28 | Layout output buffer                                           | . 37 |

| Gambar 4.29 | Layout switched capacitor cmfb                                 | 38   |

|             | Layout op-amp                                                  |      |

| Gambar 4.31 | Layout komparator                                              | 39   |

|             | Layout second-order modulator                                  |      |

| Gambar 4.33 | Grafik vinp voutp                                              | 41   |

| Gambar 4.34 | Output op-amp1                                                 | 41   |

| Gambar 4.35 | Output op-amp2                                                 | 42   |

| Gambar 4.36 | Grafik vinp-vinm dan output modulator yang sudah difilter      | 42   |

| Gambar 4.37 | Spektrum pada <i>bandwidth</i> sinyal jika gain = 0,3          | . 44 |

| Gambar 4.38 | Spektrum pada bandwidth sinyal jika gain = 0,2 dan kapasitansi |      |

|             | parasitik 0,7ff                                                | 47   |

| Gambar 4.39 | Spektrum pada bandwidth sinyal jika gain = 0,2 dan kapasitansi |      |

|             | parasitik 1ff                                                  | 47   |

| Gambar 4.40 | Spektrum pada bandwidth sinyal jika gain = 0,2 dan kapasitansi |      |

|             | parasitik 1,3ff                                                | 48   |

# **DAFTAR TABEL**

| Tabel 1 Optimasi dengan mengubah gain integrator          | 45 |

|-----------------------------------------------------------|----|

| Tabel 2 Optimasi dengan mengubah nilai kapasitansi parasi |    |

#### **BAB 1**

#### **PENDAHULUAN**

## 1.1 Latar Belakang

Dewasa ini hampir semua peralatan elektronik berbasiskan digital. Peralatan elektronik yang dulunya berbasiskan analog sekarang sudah berubah menjadi digital. Contohnya adalah kamera digital, kamera video digital, televisi digital, VOIP, dll. Bahkan media penyimpanan sekarang berbasiskan digital seperti CD, DVD, Harddisk, Flash memori yang menyimpan file gambar, video, dan suara dalam format digital. Rangkaian digital memiliki banyak kelebihan dibandingkan rangkaian analog. Rangkaian digital lebih tahan terhadap noise, sehingga rangkaian digital banyak digunakan untuk transmisi data dan penyimpanan data. Suatu musik yang ditransmisikan dalam format digital, dapat direkonstruksi kembali dengan sempurna, jika noise saat transmisi tidak mengganggu identifikasi bit 0 dan 1. Selain itu rangkaian digital dapat diimplementasikan dengan struktur yang sangat kecil dan kompleks sehingga rangkaian digital banyak digunakan untuk keperluan komputasi dan pemrosesan sinyal.

Akan tetapi, dunia fisik kita berada dalam domain analog. Tegangan, arus, suara, dll bersifat analog sehingga dibutuhkan analog to digital converter untuk mengubah sinyal – sinyal analog menjadi sinyal digital. Agar sinyal digital dapat merepresentasikan sinyal analog dengan akurat, kecepatan dan resolusi dari analog to digital converter menjadi perhatian. Umumnya terjadi pertukaran antara kecepatan dan resolusi pada analog to digital converter. Suatu arsitektur analog to digital converter yang memiliki kecepatan konversi yang tinggi seperti Flash ADC atau Pipeline ADC umumnya memiliki resolusi yang lebih rendah dibandingkan dengan arsitektur ADC dengan resolusi tinggi seperti Integrating ADC tetapi mempunyai kecepatan yang rendah.

Arsitektur ADC yang resolusinya saat ini paling tinggi adalah Delta-Sigma ADC. Delta-Sigma ADC terdiri dari Delta-Sigma Modulator dan *decimation*

filter. Skripsi ini akan membahas tentang Delta-Sigma Modulator. Untuk lebih memahami cara kerja Delta-Sigma Modulator, rangkaian dan layout integrated circuit dari second-order modulator akan simulasikan. Hasil dari simulasi akan menjelaskan dengan lebih baik cara kerja dari Delta-Sigma Modulator dan bagaimana cara mengoptimasinya agar bisa memiliki resolusi yang lebih tinggi.

#### 1.2 Tujuan

Adapun tujuan dari penulisan karya tulis ini adalah:

- Mengetahui faktor faktor yang mempengaruhi resolusi Delta-Sigma Modulator

- 2. Memahami cara pembuatan layout integrated circuit

- Mensimulasikan layout Second-Order Delta-Sigma Modulator untuk memastikan layout yang dibuat sudah benar dan untuk memahami cara kerja Second-Order Delta-Sigma Modulator

- 4. Mengoptimasi rangkaian Second-Order Delta Sigma Modulator

#### 1.3 Batasan Masalah

Penulisan skripsi dibatasi pada optimasi rangkaian digital dari Second-Order Delta-Sigma Modulator. Komponen analog Modulator, seperti op-amp dan komparator diambil dari ref. [6]. Kemudian layout keseluruhan dari Second-Order Delta Sigma Modulator, termasuk komponen analog, disimulasikan untuk mengetahui performa rangkaian. Adapun parameter yang dioptimasi adalah topologi rangkaian Modulator yang diubah menjadi fully differential dan *oversampling ratio* dari Modulator.

#### 1.4 Sistematika Penulisan

Skripsi ini terdiri dari beberapa bab yang membahas hal berikut :

### • Bab 1 Pendahuluan

Bab ini membahas tentang latar belakang, tujuan dari penulisan, batasan masalah,dan sistematika penulisan

#### Bab 2 Dasar Teori

Bab ini membahas tentang proses kuantisasi, *Signal to Noise Ratio*, *Oversampling*, CMOS, MOSIS, dan program – program yang digunakan untuk simulasi seperti LTSpice, Electric VLSI, Winspice

# • Bab 3 Delta Sigma Modulator

Bab ini menjelaskan teori Delta Sigma Modulator dan beberapa topologi rangkaiannya yaitu first-order modulator dan second-order modulator

#### Bab 4 Simulasi

Bab ini menjelaskan tentang parameter simulasi yang dilakukan, rangkaian dan layout second-order modulator yang disimulasikan, dan hasil dari simulasi

# Bab 5 Penutup

Bab ini berisi kesimpulan dari simulasi yang dilakukan dan saran untuk meningkatkan resolusi Delta-Sigma Modulator

#### **DASAR TEORI**

#### 2.1 Kuantisasi

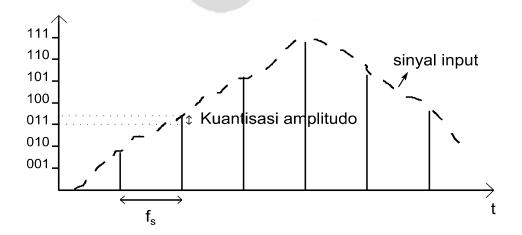

Proses pengubahan sinyal analog menjadi sinyal digital pasti melalui suatu proses kuantisasi. Proses kuantisasi tersebut dapat berupa kuantisasi amplitudo atau kuantisasi terhadap waktu. Suatu sinyal analog akan diubah menjadi n-bit sinyal digital sehingga sinyal digital akan mempunyai 2<sup>n</sup> nilai yang mungkin. Sinyal analog yang diubah akan dikuantisasi ke nilai digital yang terdekat sehingga semakin besar jumlah bit sinyal digital, semakin akurat sinyal digital tersebut merepresentasikan sinyal analog. Perbedaan nilai amplitudo antara sinyal analog asli dengan sinyal analog yang sudah dikuantisasi disebut error kuantisasi.

Selain kuantisasi amplitudo, sinyal analog juga dikuantisasi terhadap waktu. Sinyal analog melalui proses *sampling* dimana sinyal analog dikonversi pada waktu tertentu yang disebut periode *sampling*. Agar sinyal digital dapat merepresentasikan sinyal analog dengan baik, frekuensi *sampling* sinyal analog harus memenuhi kriteria nyquist yaitu frekuensi *sampling* harus lebih besar dari dua kali frekuensi terbesar sinyal analog.

$$Kriteria\ Nyquist = F_{sampling} > 2F_{max}$$

(2.1)

Gambar 2.1 Proses kuantisasi

### 2.2 Signal to Noise Ratio

Signal to Noise Ratio (SNR) adalah perbandingan nilai RMS terbesar dari sinyal terhadap nilai RMS dari noise. Nilai SNR, yang biasanya diberikan dengan satuan desibel, adalah

$$SNR(dB) = 20 \log \left( \frac{Vin(max)}{Vnoise} \right)$$

(2.2)

Nilai SNR mempunyai hubungan dengan resolusi atau jumlah bit dari suatu ADC (analog to digital converter) dimana

$$SNR = 6.02N + 1.76 \tag{2.3}$$

Dimana N adalah jumlah bit dari suatu ADC. Persamaan diatas menunjukkan nilai SNR yang harus dipenuhi oleh suatu ADC dengan jumlah bit tertentu. Misalnya suatu 16 bit ADC harus mempunyai nilai SNR = 6.02(16) + 1.76 = 98.08 dB. Selain itu, persamaan (2.3) juga dapat digunakan untuk mengetahui jumlah bit efektif yang dimiliki oleh suatu ADC dengan nilai SNR yang diukur. Dengan menulis ulang persamaan (2.3) didapatkan persamaan (2.4).

$$N_{eff} = \frac{SNR_{measured} - 1.76}{6.02} \tag{2.4}$$

## 2.3 Oversampling

Sebagian besar analog to digital converter menyampling sinyal input analog pada frekuensi nyquist, yaitu frekuensi samplingnya lebih besar dari dua kali frekuensi terbesar yang berada pada sinyal input analog. Akan tetapi sebagian ADC menyampling sinyal input pada frekuensi yang jauh lebih besar dari frekuensi nyquist. Salah satu contohnya adalah Delta Sigma ADC. Dengan

menyampling sinyal input dengan frekuensi yang jauh lebih tinggi, resolusi ADC menjadi meningkat.

Seperti telah dijelaskan sebelumnya, sinyal yang melalui proses kuantisasi pada ADC akan menimbulkan error kuantisasi. Jika sinyal analog berubah secara random dari suatu sampel ke sampel berikutnya, maka error kuantisasi mempunyai peluang yang sama berada diantara ±½LSB (least significant bit) pada output digital. Dengan asumsi diatas, error kuantisasi dapat dianggap sebagai noise kuantisasi [1]. Noise kuantisasi akan tersebar pada spektrum frekuensi nyquist.

Dengan menyampling sinyal input pada frekuensi yang jauh lebih tinggi, noise kuantisasi akan tersebar pada spektrum frekuensi yang lebih lebar sehingga noise kuantisasi akan semakin rendah.

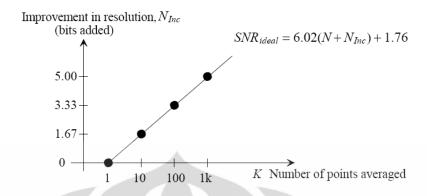

Dengan noise kuantisasi yang semakin rendah, nilai SNR akan semakin meningkat. Hubungan *oversampling ratio*, yaitu perbandingan frekuensi sampling dengan frekuensi nyquist, dengan SNR adalah

$$SNR = 6.02N + 1.76 + 10logK \tag{2.5}$$

Dimana K adalah *oversampling ratio*. Dari persamaan (2.5) diketahui bahwa setiap kenaikan dua kali lipat dari K maka SNR akan naik sebesar 3 db dan jumlah bit efektif sebesar 0,5 bit.

Gambar 2.2 Hubungan oversampling ratio dengan resolusi [1]

## **2.4 CMOS**

CMOS (Complementary metal oxide semiconductor) adalah teknologi yang umum digunakan untuk fabrikasi integrated circuit (IC). Istilah CMOS biasanya digunakan untuk suatu gaya khusus dalam mendesain rangkaian IC dan teknologi fabrikasi yang digunakan untuk memfabrikasi IC. Teknik desain rangkaian CMOS salah satunya adalah dengan menambah pasangan transistor PMOS untuk setiap NMOS. Teknik ini dapat mengurangi konsumsi daya statis dengan sangat besar [2]. Dengan konsumsi daya yang lebih rendah, CMOS juga menghasilkan panas yang lebih sedikit dibanding teknologi seperti TTL atau NMOS logic. Teknologi CMOS juga memungkinkan jumlah divais yang lebih banyak dapat difabrikasi pada suatu IC dengan ukuran tertentu. Oleh karena itu, teknologi CMOS sekarang mendominasi dalam fabrikasi integrated circuit modern. CMOS telah banyak digunakan untuk fabrikasi mikroprosesor, mikrokontroller, SRAM, digital logic, dan bahkan juga rangkaian analog seperti op-amp.

#### **2.5 MOSIS**

MOSIS (Metal Oxide Semiconductor Implementation Service) adalah sebuah layanan fabrikasi integrated circuit. MOSIS dioperasikan oleh Institut ilmu informasi di University of Southern California. MOSIS menerima design IC dari berbagai sumber seperti perusahaan dan universitas, lalu menggabungkan design tersebut dalam multiproject wafer. Biaya fabrikasi kemudian dibagi ke pengguna layanan MOSIS yang mengirim desain. Dengan membagi biaya fabrikasi, MOSIS menawarkan fabrikasi integrated circuit dalam volume rendah sampai menengah dengan harga yang lebih murah.

MOSIS menawarkan berbagai teknologi proses dari berbagai vendor seperti IBM, TSMC, On Semiconductor, dll. Pengguna layanan MOSIS dapat mendesain IC dengan *design rule* vendor yang diinginkan, atau dengan menggunakan *design rule* MOSIS yang dapat digunakan untuk semua vendor. *Design rule* MOSIS disebut SCMOS (Scalable MOS). SCMOS merupakan kumpulan layer dengan *design rule* yang dapat digunakan untuk hampir semua vendor dan semua faktor skala. Terdapat 3 jenis *design rule* SCMOS berdasarkan faktor skala yaitu SCMOS, SCMOS submicron, dan SCMOS deepsubmicron. Design rule SCMOS digunakan untuk proses 1 – 3 μm, SCMOS submicron untuk proses dibawah 1 μm, SCMOS deepsubmicron untuk proses dibawah 0,25 μm.

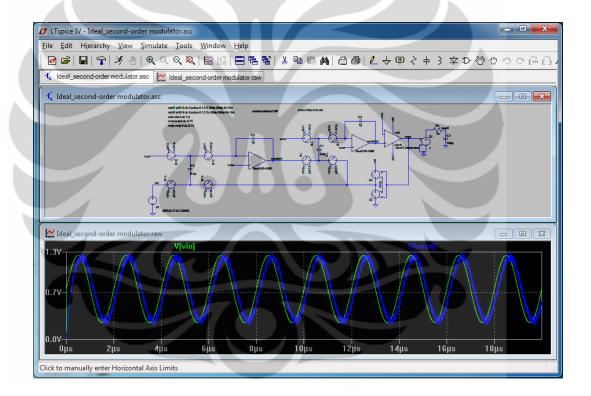

# 2.6 LTSpice

LTSpice adalah program simulasi rangkaian elektronika yang berbasis SPICE. LTSpice mempermudah simulasi menggunakan SPICE karena LTSpice adalah *schematic capture* program. Program simulasi berbasiskan SPICE lainnya mengharuskan kita memasukkan informasi rangkaian elektronik dalam bentuk kode – kode angka dan teks sehingga menjadi sangat sulit dilakukan. Akan tetapi LTSpice berbeda dengan program lainnya karena informasi rangkaian elektronik dimasukkan dalam bentuk gambar *schematic* seperti program Multisim, Proteus, dll. Oleh karena itu LTSpice menjadi sangat mudah digunakan dan user friendly.

LTSpice penulis pilih untuk mensimulasikan rangkaian dalam skripsi ini karena program ini mudah digunakan, dapat melakukan simulasi yang sangat panjang dengan rangkaian yang kompleks karena hasil simulasi disimpan ke dalam suatu file sehingga memori RAM yang kecil tidak menjadi masalah. Selain itu, program ini dapat terintegrasi dengan program Electric VLSI sehingga rangkaian dan layout yang dibuat pada program Electric VLSI dapat disimulasikan dengan menggunakan LTSpice. Program ini dapat diambil di situs www.linear.com.

Gambar 2.3 Tampilan program LTSpice

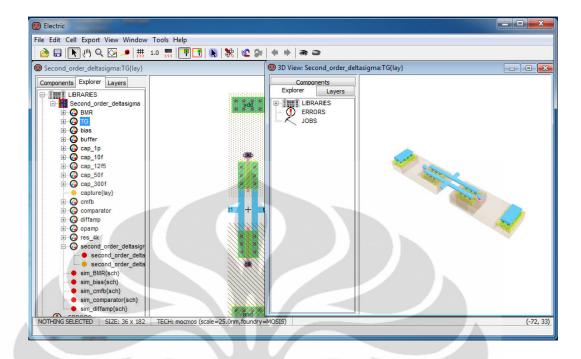

### 2.7 Electric VLSI

Electric VLSI adalah program layout editor untuk *integrated circuit*. Dengan program ini kita dapat membuat *schematic* dan layout dari rangkaian VLSI. Informasi rangkaian dimasukkan dalam bentuk gambar sama seperti program

LTSpice. Program ini juga dapat menerima *hardware description language* seperti VHDL dan Verilog.

Electric VLSI menggunakan cara yang baru dalam mengatur layout IC dibandingkan dengan program lainnya seperti Magic atau Cadence. Program ini tidak memanipulasi *polygon* pada layer – layer yang berbeda, tetapi menganggap layout sebagai kumpulan dari *nodes* dan *arcs*. *Nodes* adalah elemen rangkaian seperti transistor dan resistor sedangkan *arcs* menghubungkan node – node. Orang – orang yang belum mempunyai pengalaman dalam IC layout menemukan bahwa program Electric VLSI lebih mudah digunakan [3].

Program ini mempunyai fitur seperti design rule checking (DRC) yaitu suatu utility untuk mengecek apakah layout memenuhi design rule yang kita gunakan, layout vs schematic (LVS) yaitu suatu utility untuk membandingkan schematic dan layout dari suatu rangkaian, simulasi dengan menggunakan eksternal program seperti LTSpice. Selain itu, program ini juga mempunyai fitur 3D. Program ini dapat menampilkan layout dalam bentuk 3D. Akan tetapi program ini membutuhkan plugin tambahan agar bisa menampilkan gambar 3D.

Program ini penulis pilih untuk layout editor dari rangkaian yang akan disimulasikan karena program ini mudah digunakan. Terutama karena sistemnya yang berbeda dengan layout editor pada umumnya. Misalnya jika ingin menggambar layout transistor, kita tidak perlu lagi membuat *polygon* untuk layer active, n-select, p-select, polysilicon satu per satu melainkan cukup dengan meletakkan node transistor pada *workspace*. Program Electric VLSI akan secara otomotis menggambar layout untuk transistor dengan width/length yang kita inginkan. Program ini juga dapat menggunakan LTSpice untuk mensimulasikan layout sehingga simulasi yang kompleks menjadi lebih mudah dilakukan dengan LTSpice. Program ini bisa didapatkan dari situs www.staticfreesoft.com atau dari cmosedu.com.

Gambar 2.4 Tampilan program Electric VLSI

## 2.8 Winspice

Winspice merupakan salah satu program simulasi berbasiskan SPICE. Program ini menerima informasi rangkaian dalam bentuk kode – kode angka dan huruf sehingga program ini agak sulit digunakan. Akan tetapi program ini memungkinkan kita untuk memanipulasi data – data hasil simulasi. Karena itulah penulis menggunakan program ini yaitu untuk menghitung nilai SNR dari data – data simulasi. Program winspice mempunyai kelemahan lain yaitu tidak dapat melakukan simulasi yang panjang dan kompleks karena data simulasi disimpan dalam RAM selama simulasi dilakukan. Jika data simulasi lebih besar dari memori RAM, maka simulasi akan gagal dilakukan. Agar penulis dapat melakukan simulasi dengan program ini, maka waktu simulasi harus dipendekkan. Versi trial program ini dapat diambil di www.winspice.co.uk.

Gambar 2.5 Tampilan program Winspice

#### BAB 3

#### **DELTA SIGMA MODULATOR**

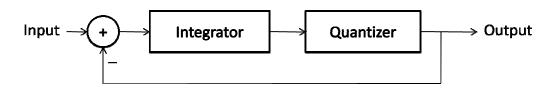

Modulasi Delta Sigma atau Delta Sigma modulation adalah suatu teknik untuk mengubah sinyal input analog menjadi sinyal digital dengan jumlah bit yang rendah. Jumlah bit yang rendah dikompensasi dengan frekuensi sampling yang lebih tinggi. Bahkan 1-bit Delta Sigma Modulator umum digunakan untuk menghasilkan lebih dari 10-bit resolusi. Densitas pulsa high pada sinyal digital merepresentasikan sinyal input analog sehingga teknik ini disebut juga sebagai pulse density modulation. Teknik ini telah banyak digunakan pada rangkaian elektronika modern seperti analog to digital converters, digital to analog converters, frequency synthesizers, switched-mode power supplies dan motor controllers [4]. Keuntungan dari Delta Sigma Modulator adalah terutama jika Delta Sigma Modulator digunakan sebagai ADC, resolusi Delta Sigma ADC lebih tinggi dibandingkan dengan jenis ADC lainnya. Akan tetapi untuk mencapai resolusi yang tinggi, maka oversampling ratio harus tinggi. Oversampling ratio yang tinggi berarti frekuensi nyquist sinyal harus rendah yang berarti bandwidth sinyal input menjadi lebih kecil.

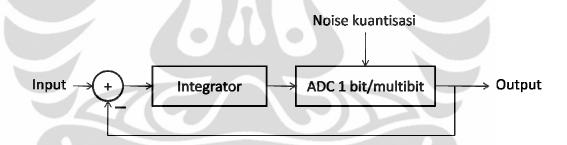

Delta Sigma Modulator terdiri dari integrator dan *quantiser*. Output dari Delta Sigma Modulator adalah sinyal digital n-bit yang tergantung dari jumlah bit *quantizer*. Rangkaian ini membandingkan sinyal input dan output yang telah dikuantisasi kemudian perbedaan dari sinyal input dan output diteruskan ke integrator. Output dari integrator kemudian dikuantisasi sehingga menghasilkan n-bit output.

Gambar 3.1 Delta Sigma Modulator

Output digital dari rangkaian Delta Sigma Modulator berbeda dengan output digital umumnya yaitu *pulse code modulation* (PCM). Hal ini karena sinyal yang dikuantisasi adalah sinyal output integrator bukan sinyal analog seperti sistem analog to digital converter seperti umumnya. Densitas pulsa high dari output Delta Sigma Modulator yang menjadi representasi sinyal input analog. Oleh karena itu jumlah bit *quantizer* tidak menjadi ukuran resolusi sinyal digital pada Delta Sigma Modulator. Bahkan *quantizer* 1-bit umum digunakan pada Delta Sigma modulator karena rangkaiannya yang lebih sederhana dan toleransi yang lebih baik terhadap variasi nilai komponen [5]. Resolusi dari Delta Sigma Modulator ditentukan oleh *oversampling ratio* dan topologi rangkaian [1].

Rangkaian Delta Sigma Modulator menggunakan frekuensi *sampling* yang jauh lebih tinggi dibandingkan kriteria nyquist. Perbandingan antara frekuensi *sampling* dengan frekuensi nyquist disebut sebagai *oversampling ratio*. Semakin tinggi *oversampling ratio*, maka resolusi Delta Sigma Modulator akan semakin meningkat.

Resolusi yang tinggi dari Delta Sigma Modulator bukan hanya disebabkan karena *oversampling ratio* yang tinggi, tetapi juga karena Delta Sigma Modulator mempunyai sifat *noise shaping*. Delta Sigma Modulator dapat menggeser noise pada frekuensi rendah ke frekuensi tinggi. Hasilnya, noise pada bandwidth sinyal menjadi berkurang. Topologi Delta Sigma Modulator menentukan sifat *noise shaping* dari modulator. Semakin banyak jumlah loop integrator, yang disebut juga orde dari modulator, maka *noise shaping* dari modulator akan semakin kuat. Second-order modulator akan memiliki resolusi yang lebih tinggi dari first-order modulator karena *noise shaping* second-order modulator lebih kuat dibandingkan first-order modulator.

#### 3.1 First-order Modulator

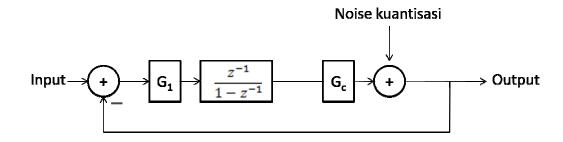

Gambar 3.2 merupakan blok diagram dari first-order modulator. First-order modulator mempunyai satu loop integrator dan *quantizer*. Blok DAC digunakan untuk memisahkan sinyal digital dengan sinyal analog. Hubungan input modulator dengan output dari modulator adalah:

$$Y(z) = z^{-1}X(z) + (1 - z^{-1})E(z)$$

(3.1)

Dimana Y(z) adalah output dari modulator, X(z) adalah input dari modulator dan E(z) adalah noise kuantisasi sebagai akibat proses kuantisasi oleh ADC. Dari persamaan (3.1) dapat dilihat bahwa output dari modulator merupakan penjumlahan dari input modulator yang mengalami *delay* dan noise kuantisasi yang mengalami differensiasi.

Gambar 3.2 Blok diagram first-order modulator

Salah satu bentuk implementasi dari first-order modulator dapat dilihat pada Gambar 3.3. Integrator diimplementasi dengan rangkaian *switched-capacitor* integrator dan *quantizer* diimplementasi dengan komparator sehingga outputnya merupakan 1-bit dengan nilai yang mungkin high dan low.

Gambar 3.3 Implementasi first-order modulator

First-order modulator merupakan topologi Delta Sigma modulator yang mempunyai *noise shaping* yang paling rendah. Oleh karena itu, resolusi dari first-order modulator lebih rendah dibandingkan dengan topologi modulator lainnya. Kenaikan resolusi jika *oversampling ratio* dinaikkan juga lebih rendah. Hubungan SNR dengan *oversampling ratio* pada first-order modulator dapat dilihat pada persamaan (3.2).

$$SNR_{ideal} = 6.02N + 1.76 - 5.17 + 30 log K$$

(3.2)

SNR pada persamaan (3.2) adalah SNR ideal. SNR tersebut adalah SNR yang dapat dicapai oleh first-order modulator dengan *oversampling ratio* K dengan komponen ideal. Komponen di dunia nyata tidaklah ideal sehingga pada prakteknya SNR yang dapat dicapai akan lebih rendah dibandingkan dengan persamaan (3.2). Kenaikan resolusi terhadap *oversampling ratio* pada first-order modulator dapat dilihat pada Gambar 3.4. Dapat dilihat first-order modulator, karena mempunyai *noise shaping*, mempunyai kenaikan resolusi yang lebih besar dibandingkan *oversampling* biasa.

Gambar 3.4 Kenaikan resolusi terhadap *oversampling ratio* pada first-order modulator

First-order modulator dapat direpresentasikan dengan model linear seperti Gambar 3.5. Gain forward dari modulator adalah :

$$G_F = G_1.G_c \tag{3.3}$$

Dimana G<sub>F</sub> adalah *forward gain*, G<sub>1</sub> adalah gain dari integrator dan G<sub>c</sub> adalah gain dari *quantizer*. Persamaan (3.1) dapat ditulis ulang menjadi

$$Y(z) = \frac{z^{-1}G_F}{1 + Z^{-1}(G_F - 1)}X(z) + \frac{1 - Z^{-1}}{1 + Z^{-1}(G_F - 1)}E(z)$$

(3.4)

Dari persamaan (3.4) nilai *forward gain* dapat dibatasi agar sistem menjadi stabil.

$$0 \le G_F \le 2 \tag{3.5}$$

Gambar 3.5 Model linear first-order modulator

#### 3.2 Second-order Modulator

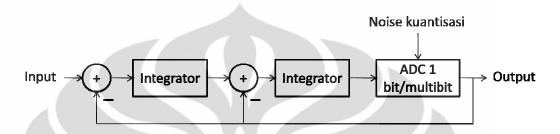

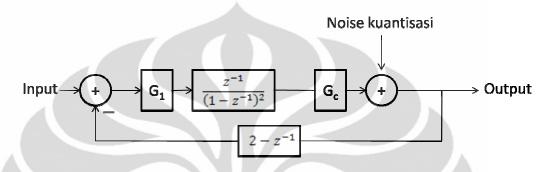

Second-order Modulator mempunyai dua loop integrator dan satu *quantizer* seperti pada Gambar 3.6.

Gambar 3.6 Second-order modulator

Second-order Modulator mempunyai tambahan loop integrator sehingga noise shaping second-order modulator lebih baik dibandingkan dengan first-order modulator. Hubungan output dengan input modulator pada second-order modulator adalah

$$Y(z) = z^{-1}X(z) + (1 - z^{-1})^{2}E(z)$$

(3.6)

Dari persamaan (3.6) dapat dilihat bahwa noise kuantisasi E(z) mengalami differensiasi dua kali sehingga resolusi second-order modulator lebih tinggi dibandingkan first-order modulator. Implementasi dari second-order modulator terdapat pada Gambar 3.7. Dimana integrator diimplementasikan dengan *switched capacitor* integrator dan *quantizer* dengan komparator.

Gambar 3.7 Implementasi second-order modulator

Kenaikan resolusi terhadap *oversampling ratio* pada second-order modulator juga lebih tinggi. Hubungan SNR dengan *oversampling ratio* adalah

$$SNR_{ideal} = 6.02N + 1.76 - 12.9 + 50logK \tag{3.7}$$

Dari Gambar 3.8 dapat dilihat bahwa kenaikan resolusi pada second-order modulator lebih besar dibandingkan dengan first-order modulator. Untuk mencapai resolusi yang sama, *oversampling ratio* dari second-order modulator menjadi lebih kecil sehingga *bandwidth* sinyal menjadi lebih besar.

Gambar 3.8 Kenaikan resolusi terhadap *oversampling ratio* pada second-order modulator

Model linear dari second-order modulator dapat dilihat pada Gambar 3.9. Gain forward dari modulator adalah :

$$G_F = G_1.G_c \tag{3.8}$$

Gambar 3.9 Model linear dari second-order modulator

Persamaan (3.6) dapat ditulis ulang menjadi:

$$Y(z) = \frac{G_F z^{-1}}{1 + z^{-1} 2(G_F - 1) + z^{-2} (1 - G_F)} X(z) + \frac{(1 - z^{-1})^2}{1 + z^{-1} 2(G_F - 1) + z^{-2} (1 - G_F)} E(z)$$

(3.9)

Dengan menyelesaikan persamaan (3.6) didapatkan jangkauan nilai gain agar modulator stabil yaitu

$$0 \le G_F \le 1.333 \tag{3.10}$$

#### BAB 4

#### **SIMULASI**

Pada skripsi ini, penulis akan mensimulasikan rangkaian dan layout integrated circuit dari second-order Delta Sigma modulator. Simulasi akan dilakukan dengan program LTSpice dan Winspice sedangkan program Electric VLSI akan digunakan untuk editor schematic dan layout integrated circuit. Schematic dan layout dari second-order modulator akan diedit gambarnya dengan menggunakan Electric VLSI. Kemudian program Electric akan meng-export kode SPICE dari gambar schematic dan layout untuk kemudian disimulasikan dengan menggunakan LTSpice. Program Winspice digunakan untuk menghitung SNR dari rangkaian second-order modulator yang telah dibuat.

Model transistor yang digunakan dalam simulasi ini adalah model BSIM4 untuk proses 50 nm dengan power supply VDD = 1 volt. Model ini digunakan karena rangkaian yang akan disimulasikan diambil dari ref. [1] dan [6] dan modelnya adalah BSIM4. Sedangkan untuk layout, *design rule* yang digunakan adalah SCMOS (Scalable CMOS) deepsubmicron yang berasal dari MOSIS. *Design rule* ini merupakan *design rule* abstrak yang dapat digunakan untuk proses - proses semikonduktor yang didukung oleh MOSIS. Dengan menggunakan *design rule* ini layout yang dibuat tidak hanya terikat pada satu proses saja, tetapi dapat digunakan untuk proses semikonduktor lainnya dengan mengubah faktor skala λ. *Design rule* ini tediri dari 3 jenis, yaitu SCMOS, SCMOS submicron dan SCMOS deepsubmicron. Design rule yang digunakan adalah SCMOS deepsubmicron karena model transistor yang digunakan untuk ukuran 50 nm.

Editor yang digunakan untuk membuat *schematic* dan layout second-order modulator adalah Electric VLSI. Faktor skala  $\lambda$  yang digunakan adalah 25 nm. Berdasarkan *design rule* dari MOSIS, minimum length dari gate transistor adalah  $2\lambda$  [7]. Sedangkan rangkaian second-order modulator yang digunakan mempunyai minimum length dari transistornya 50 nm. Oleh karena itu skala  $\lambda$  yang digunakan

adalah 25 nm untuk menyesuaikan *design rule* MOSIS dengan rangkaian yang sudah ada.

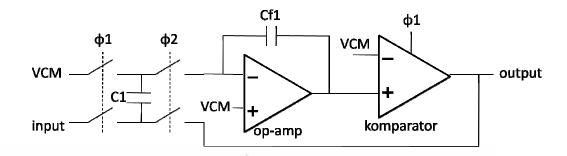

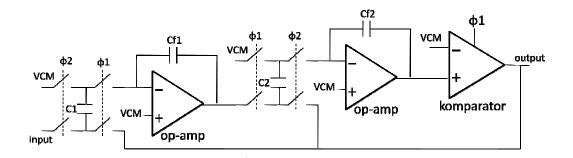

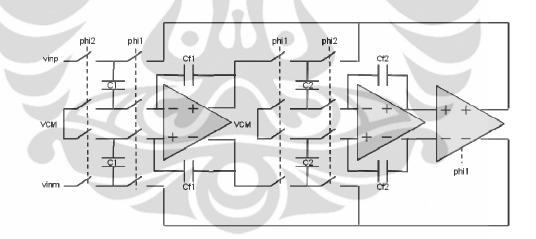

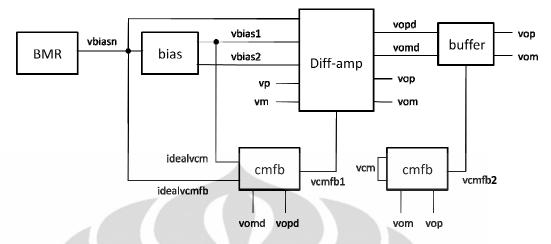

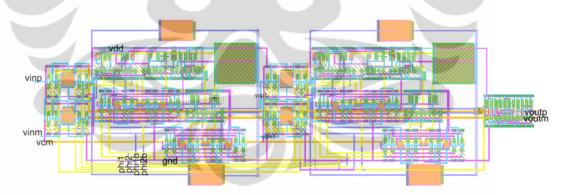

### 4.1 Rangkaian

Rangkaian second-order modulator yang akan disimulasikan hampir sama dengan rangkaian second-order modulator pada bab sebelumnya (Gambar 3.7). Akan tetapi berdasarkan ref. [1], topologi *fully differential* dapat mengurangi noise dan distorsi yang disebabkan oleh komponen yang tidak ideal, sinyal clock dan power supply yang tidak stabil. Oleh karena itu rangkaian second-order modulator pada Gambar 3.7 diubah menjadi rangkaian *fully differential* second-order modulator seperti pada Gambar 4.1.

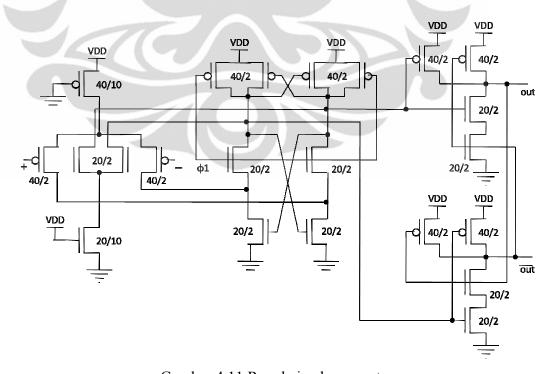

Gambar 4.1 Rangkaian simulasi second-order modulator

Rangkaian ini terdiri dari dua *fully differential switched capacitor* integrator dan satu komparator sebagai ADC 1-bit. Input dari modulator adalah vinp dan vinm sedangkan output dari modulator adalah output dari komparator. Gain dari integrator adalah perbandingan dari kapasitor pada input op-amp dan kapasitor feedback op-amp. Gain integrator pertama adalah  $G_1 = \frac{C1}{Cf1}$  dan gain integrator

kedua adalah  $G_2 = \frac{C2}{Cf2}$ . Untuk simulasi awal, nilai  $G_1$  dan  $G_2$  dipilih 0,3 yang berarti nilai  $C_1$ , $C_2$  adalah 0,3pf dan nilai Cf1,Cf2 adalah 1pf.

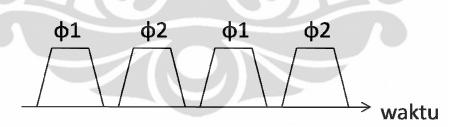

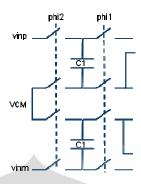

Rangkaian ini menggunakan 4 sinyal clock yaitu phi1, phi1b, phi2, phi2b. Clock phi1 dan phi2 merupakan clock untuk gate NMOS sedangkan clock phi1b (kebalikan dari clock phi1) dan clock phi2b (kebalikan dari clock phi2) merupakan clock untuk gate PMOS. Clock phi1 dan phi2 sendiri merupakan clock nonoverlapping yang berarti clock ini tidak akan bernilai high pada saat yang bersamaan. Untuk lebih jelasnya perhatikan Gambar 4.2. Dari gambar tersebut dapat dilihat clock tersebut tidak bernilai high pada saat yang bersamaan. Antara nilai clock phi1 berubah menjadi low dan nilai clock phi2 berubah menjadi high terdapat delay waktu untuk memastikan nilai kedua clock tidak high bersamaan. Jika kedua clock high bersamaan, switch yang dikontrol oleh clock tersebut akan short secara bersamaan sehingga input dari op-amp akan berhubungan langsung dengan tegangan VCM (VCM adalah setengah dari VDD) yang tentu saja tidak diinginkan. Berdasarkan diagram second-order modulator pada Gambar 3.6, input op-amp seharusnya adalah perbedaan dari input dan output modulator.

Gambar 4.2 *Nonoverlapping* clock

Berikut ini akan dijelaskan komponen – komponen dari rangkaian secondorder modulator yang akan disimulasikan :

### • Switch

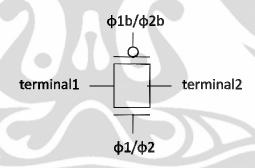

Switch diimplementasi dengan *transmission gate*, yaitu gabungan dari NMOS dan PMOS. Transmission gate berguna untuk menahan atau melewatkan sinyal yang dikontrol oleh sinyal pada gate NMOS dan PMOS. Transistor NMOS dan PMOS digunakan sekaligus karena NMOS baik dalam melewatkan sinyal low sedangkan jelek ketika melewatkan sinyal high. Begitu juga sebaliknya, PMOS baik dalam melewatkan sinyal high. Ketika keduanya digabungkan, didapatkan rangkaian *transmission gate* yang baik dalam melewatkan sinyal low dan high. NMOS dikontrol oleh clock phi1 atau phi2 dan PMOS dikontrol oleh clock phi1b atau phi2b. Gambar *transmission gate* dapat dilihat pada Gambar 4.3. PMOS dan NMOS pada *transmission gate* mempunyai ukuran transistor *width/length* = 20/2 dengan faktor skala  $\lambda = 25$  nm.

Gambar 4.3 Transmission gate

## • Rangkaian switched capacitor

Rangkaian ini berguna untuk mencari perbedaan tegangan input dan output dari modulator. Rangkaian ini terdiri dari switch dan kapasitor. Mekanisme rangkaian ini adalah penyimpanan muatan di kapasitor. Ketika salah satu switch ditutup selama suatu waktu yang ditentukan oleh periode sampling, muatan akan mengalir ke kapasitor. Muatan ini kemudian akan mengalir ke op-amp ketika switch lain ditutup sebagai perbedaan dari input dan output modulator.

Gambar 4.4 Switched capacitor

# • Op-amp

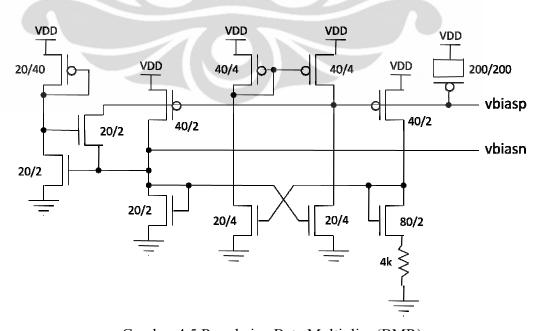

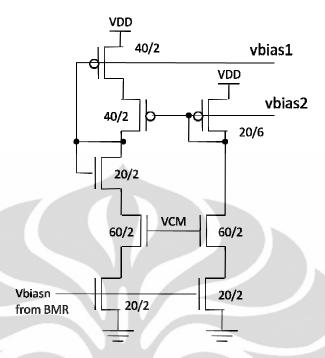

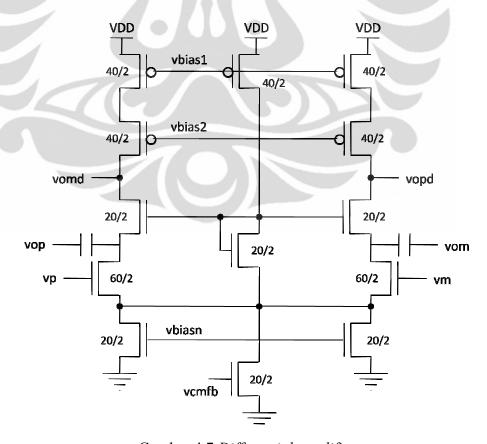

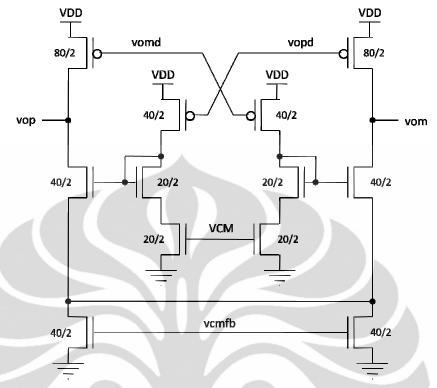

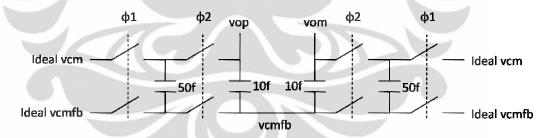

Rangkaian op-amp pada simulasi ini diambil dari buku CMOS Circuit Design, Layout, and Simulation [6]. O-amp ini didesain khusus untuk rangkaian *switched capacitor*. Op-amp ini menggunakan *switched capacitor* CMFB. Rangkaian CMFB menggunakan *transmission gates*, oleh karena itu rangkaian op-amp ini memerlukan sinyal clock juga. Rangkaian op-amp terdiri dari rangkaian biasing, *differential amplifier*, *output buffer*, dan *switched capacitor* CMFB. Dibawah ini adalah gambar dari semua rangkaian tersebut.

Gambar 4.5 Rangkaian Beta Multiplier (BMR)

Gambar 4.6 Rangkaian biasing

Gambar 4.7 Differential amplifier

Gambar 4.8 Output buffer

Gambar 4.9 Switched capacitor CMFB

Gambar 4.10 Rangkaian fully differential op-amp

# • Komparator

Rangkaian komparator yang digunakan juga diambil dari buku CMOS Circuit Design, Layout, and Simulation. Berikut adalah rangkaian dari komparator

Gambar 4.11 Rangkaian komparator

Selain menggunakan topologi *fully differential*, rangkaian second-order modulator juga dioptimasi dengan menaikkan *oversampling ratio*. *Oversampling ratio* bisa dinaikkan dengan cara menaikkan frekuensi sampling rangkaian, yaitu frekuensi clock phi pada rangkaian, atau dengan menurunkan bandwidth sinyal, yang dapat dilakukan pada simulasi karena output dari modulator tidak melalui filter digital. Pada skripsi ini, *oversampling ratio* dilakukan dengan menurunkan bandwidth sinyal hingga pada 781250Hz sehingga dengan frekuensi sampling 100 MHz, *oversampling ratio* menjadi 100MHz/(2\*781250Hz) = 64.

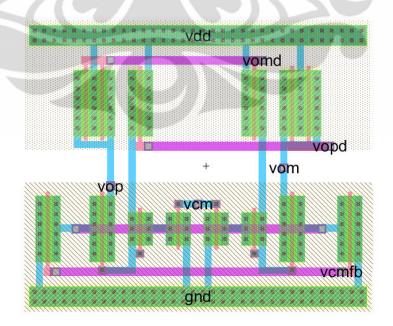

## 4.2 Layout

Rangkaian second-order modulator diatas akan dibuat layoutnya dengan menggunakan program Electric VLSI. Pembuatan layout *integrated circuit* dari suatu rangkaian terdiri dari beberapa layer yang berfungsi sebagai *masking* pada proses pembuatan *integrated circuit*. Biasanya untuk membentuk suatu komponen seperti transistor atau kapasitor dibutuhkan lebih dari satu layer. Proses pembuatan layout CMOS adalah dua dimensi. Layer – layer tersebut sudah ditentukan tinggi, urutannya, materialnya oleh perusahaan fabrikasi sehingga seorang designer hanya bisa mengatur bentuk dua dimensi pada tiap layer. Program Electric VLSI sangat membantu proses pembuatan layout karena untuk komponen seperti transistor, bentuk umum dari layout transistor dapat digenerate secara otomatis. Kita hanya perlu mengubah width/height dari layout transistor tersebut. Adapun layer – layer yang digunakan dalam proses pembuatan layout second-order modulator adalah:

#### P-Well

P-Well merupakan layer silicon tipe-p yang digunakan sebagai tempat meletakkan transistor NMOS. Pada program Electric VLSI, layer P-Well direpresentasikan dengan arsiran seperti pada Gambar 4.12

Gambar 4.12 Layer P-Well

### • N-Well

N-Well merupakan layer silicon tipe-n yang digunakan sebagai tempat meletakkan transistor PMOS. Layer N-Well juga digunakan sebagai resistor.

Gambar 4.13 Layer N-Well

### Active

Layer active digunakan untuk mendefinisikan *opening* atau bagian yang akan di etch dari silicon dioxide. Biasanya layer active digunakan untuk membentuk source dan drain dari MOSFET.

Gambar 4.14 Layer active

## • Layer p-select

Digunakan untuk menentukan bagian mana yang akan didoping dengan atom *acceptor*. Biasanya digunakan untuk mendoping layer active agar menjadi source dan drain dari PMOS.

Gambar 4.15 Layer p-select

## • Layer n-select

Digunakan untuk menentukan bagian mana yang akan didoping dengan atom donor. Biasanya digunakan untuk mendoping layer active agar menjadi source dan drain dari NMOS.

Gambar 4.16 Layer n-select

# Layer polysilicon1

Layer ini digunakan untuk membentuk gate dari MOSFET. Selain itu, layer ini juga digunakan untuk membentuk poly1-poly2 kapasitor.

Gambar 4.17 Layer polysilicon1

## Layer polysilicon2

Layer ini digunakan untuk membentuk poly1-poly2 kapasitor. Layer polysilicon2 terletak diatas polysilicon1.

Gambar 4.18 Layer polysilicon2

## Layer metal

Layer metal digunakan untuk sebagai konduktor untuk menghubungkan antara komponen pada layout. Layer metal berjumlah 5 agar *routing* dari layout menjadi lebih mudah. Untuk menghubungkan antara layer metal dan antara layer active dengan metal digunakan layer via.

Gambar 4.19 Layer metal 1-5 (dari kiri ke kanan).

Gambar 4.20 Layer via

Untuk memudahkan proses pembuatan layout, sebuah frame standar dibuat untuk memudahkan koneksi dari body transistor ke vdd atau ground [6]. Frame standar tersebut dapat dilihat pada Gambar 4.21. Bagian yang diarsir di bagian atas frame yaitu n-well adalah tempat PMOS diletakkan sedangkan bagian bawahnya yaitu p-well adalah tempat NMOS diletakkan. Bagian warna hijau adalah layer active dan layer metal yang berhimpit dengan layer metal diatas layer active dan antara layer metal dan layer active dihubungkan oleh layer via. Frame ini memudahkan koneksi body PMOS ke vdd atau body NMOS ke ground.

Gambar 4.21 Frame standar untuk layout

Sedangkan untuk komponen yang bukan transistor, seperti resistor dan kapasitor layoutnya adalah sebagai berikut :

Gambar 4.22 Layout n-well resistor

Gambar 4.23 Layout poly1-poly2 kapasitor

Layout resistor dibuat dari n-well, dengan nilai resistor didapat dari perbandingan length dengan width dari n-well dikali dengan n-well *sheet resistance* yaitu resistansi material jika length/width = 1. Nilai n-well *sheet resistance* biasanya didapat dari perusahaan fabrikasi, tetapi untuk skripsi ini nilai n-well *sheet resistance* diambil dari ref. [6] yaitu adalah 2kΩ/square. Selanjutnya, layout kapasitor sama seperti kapasitor 2 keping sejajar, dimana keping diatas adalah layer polysilicon2 yang berwarna oranye dan keping bawah adalah layer polysilicon1 yang berwarna pink sedangkan layer yang berwarna biru tua adalah layer metal1. Nilai kapasitor dihitung dari luas daerah pada pertemuan layer poly1-poly2 dikali dengan kapasitansi oxide per area. Antara layer poly1-poly2 dibatasi dengan oxide dengan tebal yang telah ditentukan sehingga nilai kapasitor hanya bisa diubah dengan mengubah luas permukaan kapasitor Nilai kapasitansi oxide per area diambil dari ref. [6] yaitu adalah 25fF/μm² untuk proses 50 nm. Selain itu nilai kapasitansi parasitik dari layer poly1 ke substrat harus

diperhitungkan yaitu adalah 58aF/µm² plate capacitance dan 88aF/µm² fringe capacitance. Sehingga nilai kapasitansi parasitik poly1 adalah luas daerah poly1 dikali dengan plate capacitance ditambah dengan keliling poly1 dikali dengan fringe capacitance.

Layout dari second-order modulator dibuat dengan meletakkan transistor – transistor NMOS dan PMOS pada frame standar, kemudian komponen resistor dan kapasitor diluar frame standar, dan kemudian menghubungkan komponen dengan layer metal. Layer metal yang digunakan adalah layer metal 1 sampai dengan layer metal 5. Pada layout, jalur metal yang mehubungkan komponen tidak boleh tumpang tindih dengan jalur metal lainnya. Oleh karena itu digunakan banyak layer metal agar tidak ada jalur metal yang bersentuhan. Berikut adalah layout dari tiap rangkaian yang sudah dijelaskan diatas :

• Layout transmission gate

Gambar 4.24 Layout transmission gate

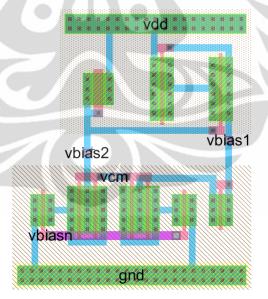

• Layout rangkaian beta-multiplier

Layout rangkaian beta-multiplier mempunyai sebuah transistor dengan ukuran yang besar yaitu 200/200 sehingga hampir setengah dari layout dipenuhi oleh transistor tersebut (transistor yang terletak disebelah kanan layout).

Gambar 4.25 Layout beta-multiplier

• Layout rangkaian bias

Gambar 4.26 Layout rangkaian bias

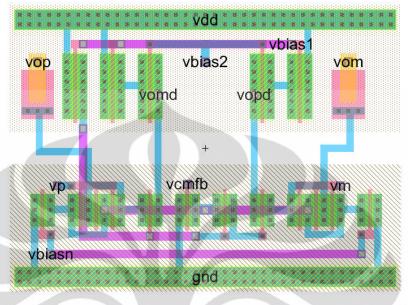

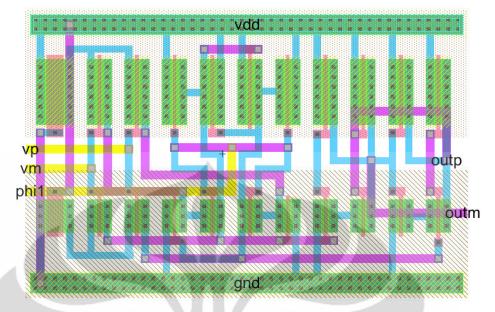

# • Layout differential amplifier

Gambar 4.27 Layout rangkaian differential amplifier

• Layout output buffer

Gambar 4.28 Layout rangkaian output buffer

• Layout switched capacitor cmfb

Gambar 4.29 Layout switched capacitor cmfb

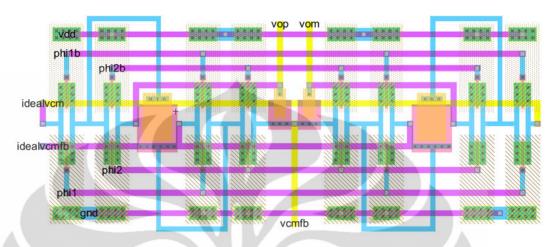

• Layout keseluruhan op-amp

Gambar 4.30 Layout op-amp

Gambar 4.31 Layout komparator

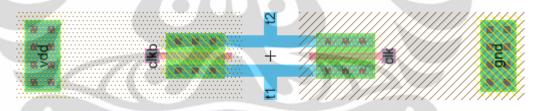

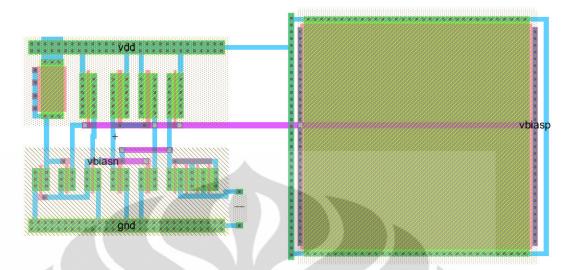

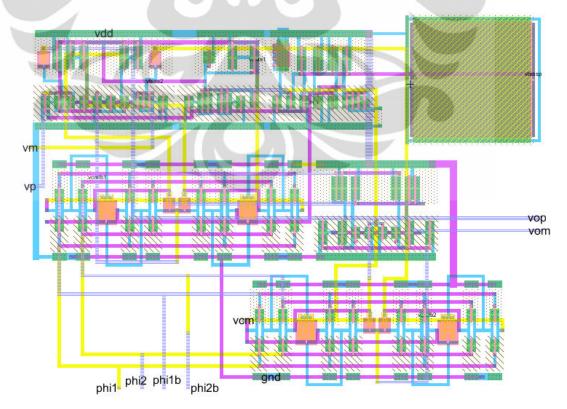

Adapun jumlah transistor dalam layout yang dibuat adalah 208 transistor dengan luas area layout adalah 65 x 21 µm. Layout keseluruhan dari rangkaian second-order modulator dapat dilihat pada Gambar 4.32.

Gambar 4.32 Layout second-order modulator

### 4.3 Hasil simulasi

Layout yang telah dibuat dengan menggunakan program Electric kemudian disimulasikan dengan menggunakan LTSpice. Berikut adalah parameter simulasi yang dilakukan dalam kode SPICE :

vdd vdd 0 dc 1

vem vem 0 dc 0.5

vphi1 phi1 0 dc 0 pulse 0 1 0 200p 200p 4n 10n

vphi2 phi2 0 dc 0 pulse 0 1 5n 200p 200p 4n 10n

vphi1b phi1b 0 dc 0 pulse 1 0 0 200p 200p 4n 10n

vphi2b phi2b 0 dc 0 pulse 1 0 5n 200p 200p 4n 10n

vinp vinp 0 dc 0 sin 0.5 0.4 500KHz

vinm vinm 0 dc 0 sin 0.5 -0.4 500KHz

E1 vout 0 voutp voutm 1

R1 voutf vout 1k

C1 voutf 0 100p

.tran .1n 20u uic

Baris pertama dan kedua mendefinisikan tegangan vdd dan vcm (tegangan yaitu 1 volt. setengah vdd) volt dan 0.5 Selanjutnya vphi1,vphi2,vphi1b,vphi2b adalah sinyal clock yang mengatur frekuensi sampling dari rangkaian second-order modulator. Periode dari sinyal clock adalah 10 ns yang berarti frekuensi sampling dari modulator adalah 100 MHz. Vinp dan vinm adalah sinyal input dari modulator. Modulator menggunakan topologi fully differential sehingga input dari modulator merupakan selisih dari vinp dan vinm dan output dari modulator adalah selisih dari voutp dan voutm. Baris selanjutnya, komponen E, R, dan C digunakan untuk membangun RC lowpass filter sederhana untuk memfilter output dari modulator. Output dari modulator seharusnya difilter dengan decimation filter untuk mendapatkan output digital dengan jumlah bit yang banyak. Akan tetapi, jika output dari modulator difilter dengan filter analog maka jika modulator tersebut ideal, output dari filter tersebut akan menyerupai sinyal input dari modulator. Untuk mengetahui modulator dapat bekerja dengan baik, maka output dari modulator difilter dengan RC filter sederhana untuk melihat apakah output dari filter sama dengan input dari modulator. Baris terakhir, adalah jenis simulasi yang dilakukan yaitu simulasi transien dengan lama simulasi 20 us dengan step time 0,1 ns.

Berikut adalah hasil simulasi dengan menggunakan LTSpice :

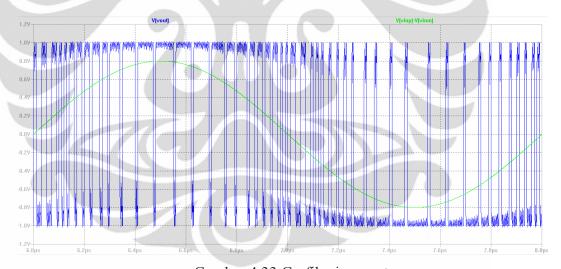

Gambar 4.33 merupakan grafik input dan output dari modulator. Input dari modulator adalah grafik warna hijau merupakan selisih dari vinp dan vinm dan output dari modulator adalah grafik warna biru merupakan selisih dari voutp dan voutm. Input dari modulator merupakan sinyal sinusoidal dengan amplitudo 0,8 volt dan output dari modulator merupakan sinyal digital 1 bit dengan nilai 1 volt atau -1 volt. Dapat dilihat jika sinyal input berada pada amplitudo positif maksimum, maka output dari modulator akan lebih banyak high daripada low sedangkan jika amplitudo sinyal input negatif maksimum, maka output dari modulator akan lebih banyak low. Jika amplitudo sinyal input 0 volt, maka high dan low dari output modulator akan seimbang. Pada output dari modulator dapat dilihat adanya noise yang muncul akibat sinyal clock.

Gambar 4.33 Grafik vinp voutp

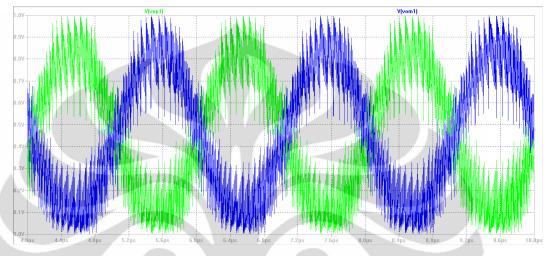

Gambar 4.34 merupakan output dari integrator pertama pada rangkaian second-order modulator. Jika gain dari integrator pertama terlalu besar, maka output dari integrator pertama akan saturasi. Ayunan maksimum dari output integrator berada pada 1 volt hingga -1 volt. Jika ayunan output integrator lebih besar dari ayunan maksimum, akan terjadi saturasi sehingga modulator tidak akan berkerja sebagaimana mestinya. Dari grafik diatas dapat dilihat bahwa output dari

integrator tidak mengalami saturasi. Demikian juga dengan output integrator kedua pada Gambar 4.35. Agar modulator dapat bekerja dengan baik, gain dari integrator harus diperhatikan agar modulator stabil dan output dari integrator tidak mengalami saturasi.

Gambar 4.34 Output op-amp 1

Gambar 4.35 Output op-amp 2

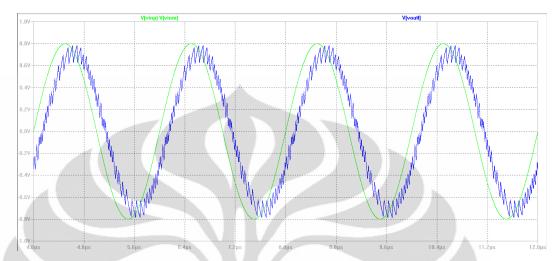

Gambar 4.36 merupakan grafik dari input modulator dan output yang telah difilter. Grafik warna hijau merupakan input dari modulator dan grafik warna biru merupakan output modulator yang telah difilter. Dapat dilihat bahwa output digital yang telah difilter menyerupai sinyal input. Hal ini berarti modulator telah

bekerja dengan baik. Karena filter yang digunakan adalah filter RC sederhana, maka pada sinyal yang telah difilter masih terdapat komponen frekuensi tinggi.

Gambar 4.36 Grafik vinp-vinm dan output modulator yang sudah difilter

Selain simulasi dengan LTSpice, rangkaian second-order modulator juga disimulasikan dengan Winspice untuk menghitung SNR dari modulator. Program Winspice memungkinkan memanipulasi data hasil simulasi sehingga program Winspice digunakan untuk memanipulasi data untuk menghitung SNR. Berikut adalah tambahan parameter simulasi ketika simulasi dengan menggunakan Winspice:

```

.tran 5n 20u uic

plot vout

linearize vout

spec 0 781250 100k vout

let voutdb=db(mag(vout))

plot voutdb ylimit -100 0

let m=mag(vout)

let m[0]=0

let m[5]=0

let qdnoise=0.707*sqrt(mean(m*m)*length(m))

```

print qdnoise

let SNRD=db((0.8/sqrt(2))/qdnoise)

print SNRD

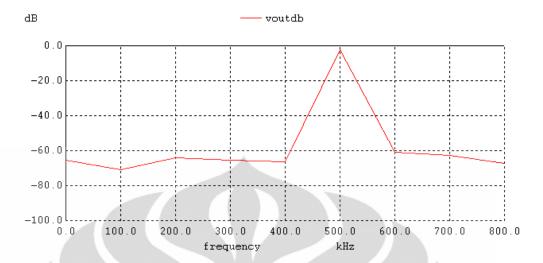

Untuk menghitung SNR, dipilih *oversampling ratio* sebesar 64. Dengan frekuensi *sampling* 100 MHz berarti *bandwidth* sinyal adalah sebesar  $\frac{100MHz}{2x64}$  yaitu 781250 Hz. Untuk menghitung SNR, pertama – tama output modulator diubah ke domain frekuensi dengan *discrete fourier transform*. Perintah 'spec 0 781250 100k vout' mengubah sinyal vout ke domain frekuensi dari 0 sampai 781250Hz dengan frekuensi step 100KHz. Semakin kecil frekuensi step, semakin lama simulasi yang perlu dilakukan sehingga 100KHz dipilih agar simulasi tidak menjadi terlalu lama. Setelah itu, komponen frekuensi dc dan sinyal input dihilangkan dengan perintah 'm[0]=0' dan 'm[5]=0'. Setelah itu noise rangkaian dicari nilai rms nya yaitu 'qdnoise'. Setelah itu SNR dihitung dengan membagi nilai rms sinyal dengan nilai rms noise. Berikut adalah hasil simulasi dengan menggunakan winspice:

snrd = 54.01 dB

SNR yang didapat adalah 54,01 dB. Sebenarnya yang dihitung pada simulasi ini adalah SNRD yaitu Signal to Noise Ratio plus Distortion. SNRD juga termasuk distorsi akibat ketidakidealan rangkaian. Dengan SNR 54,01 dB, bit effektif modulator dapat dihitung dengan persamaan (2.4) yaitu adalah 8,6 bit atau 8 bit. Bit efektif ini melambangkan resolusi dari modulator. Sedangkan Gambar 4.37 adalah hasil *discrete fourier transform* dari output modulator pada *bandwidth* sinyal. Dapat dilihat komponen frekuensi 500 KHz adalah frekuensi sinyal input.

Gambar 4.37 Spektrum pada bandwidth sinyal jika gain = 0,3

## 4.3 Optimasi

Layout second-order Delta Sigma Modulator akan dioptimasi dengan mengubah nilai kapasitor C1, C2 sehingga nilai gain integrator berubah. Nilai gain dari integrator akan diubah mulai dari 0,1 sampai 0,4, kemudian layout tersebut akan disimulasikan untuk melihat pengaruh perubahan nilai integrator terhadap performance dari rangkaian, khususnya resolusi dari modulator.

Kapasitor pada layout second-order Modulator ini dibuat dengan kapasitor keping sejajar layer poly1 dan poly2 seperti pada Gambar 4,23. Oleh karena itu, nilai kapasitansi parasitik antara layer poly1 tidak dapat dihindari. Simulasi layout dari second-order modulator dilakukan dengan memperhitungkan nilai kapasitansi parasitik ini. Layout pada Gambar 4.32 akan dibuat dengan editor Electric VLSI kemudian nilai SNR dari modulator akan dihitung dengan menggunakan program Winspice. Optimasi pertama dapat dilihat pada tabel 1:

Tabel 1 Optimasi dengan mengubah gain integrator

| No. | C1(pf) | C2(pf) | C <sub>parasitik</sub> 1(ff) | C <sub>parasitik</sub> 2(ff) | SNR(dB) |

|-----|--------|--------|------------------------------|------------------------------|---------|

| 1   | 0,1    | 0,1    | 0,4                          | 0,4                          | 61,76   |

| 2   | 0,2    | 0,2    | 0,7                          | 0,7                          | 65,92   |

| 3   | 0,3    | 0,3    | 0,91                         | 0,91                         | 54,01   |

| 4   | 0,4    | 0,4    | 1,25                         | 1,25                         | 57,77   |

Pada optimasi ini, nilai kapasitor feedback Cf1,Cf2 adalah tetap 1pf dengan kapasitansi parasitik 2.83ff. Nilai C1 dan C2 diubah – ubah sehingga gain dari integrator berubah untuk melihat pengaruhnya terhadap resolusi dari modulator. Dari hasil simulasi pada tabel 1 dapat dilihat bahwa resolusi dari modulator yaitu nilai SNR dari modulator paling baik ketika nilai kapasitor C1 dan C2 adalah 0,2 pf. Hal ini berarti gain integrator yang paling baik adalah C1,C2 / Cf1,Cf2 yaitu adalah 0,2.

Selanjutnya, nilai kapasitansi parasitik poly1 ke substrat dari kapasitor diubah – ubah dengan nilai kapasitor C1 dan C2 tetap yaitu 0,2pf. Simulasi ini dilakukan untuk melihat pengaruh nilai kapasitansi parasitik terhadap resolusi dari modulator. Optimasi kedua dapat dilihat pada tabel 2.

Tabel 2 Optimasi dengan mengubah nilai kapasitansi parasitik

| No. | C1, C2 (pf) | C <sub>parasitik</sub> 1, C <sub>parasitik</sub> 2(ff) | SNR(dB) |

|-----|-------------|--------------------------------------------------------|---------|

| 1   | 0,2         | 1f                                                     | 93,08   |

| 2   | 0,2         | 1,3f                                                   | 69,41   |

| 3   | 0,2         | 1,6f                                                   | 65,22   |

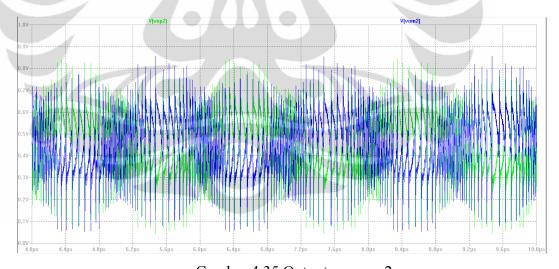

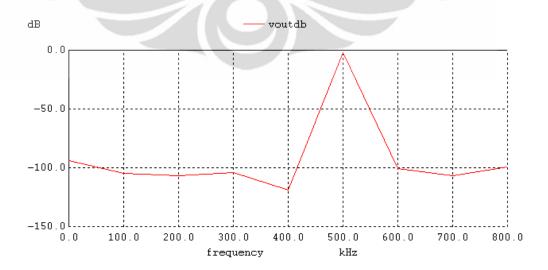

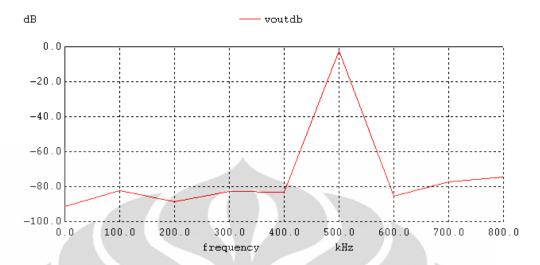

Pada tabel 2, dapat dilihat jika nilai kapasitansi parasitik berubah, terutama pada data no. 1 dan 2, nilai SNR lebih baik dibandingkan dengan nilai SNR pada tabel 1. Bahkan ketika nilai kapasitansi parasitik 1ff, nilai SNR meningkat drastis menjadi 93.08 dB yang berarti resolusi dari modulator menjadi 15 bit. Padahal ketika nilai kapasitansi berbeda 0,3ff yaitu ketika nilai kapasitansi parasitik 0,7ff

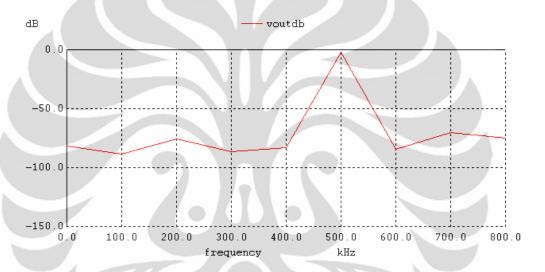

dan 1.3ff, nilai SNR berkisar antara 65.92 dB dan 69.41 dB. Untuk lebih jelas, perhatikan spektrum pada bandwidth sinyal ketika kapasitansi parasitik 0,7ff, 1ff, dan 1,3ff.

Dari Gambar 4.38, 4.39, 4.40 dapat dilihat bahwa noise pada bandwidth sinyal jika kapasitansi parasitik 1ff lebih rendah. Frekuensi sinyal input adalah 500KHz sehingga perbandingan antara komponen sinyal dengan noise melambangkan resolusi dari modulator.

Gambar 4.38 Spektrum pada bandwidth sinyal jika gain = 0,2 dan kapasitansi parasitik 0,7ff

Gambar 4.39 Spektrum pada bandwidth sinyal jika gain = 0,2 dan kapasitansi parasitik 1ff

Gambar 4.40 Spektrum pada bandwidth sinyal jika gain = 0,2 dan kapasitansi parasitik 1,3ff

### **BAB 5**

### **KESIMPULAN**

Delta-Sigma Modulator merupakan suatu rangkaian yang mengubah sinyal input analog menjadi sinyal digital dengan jumlah bit yang rendah. Bahkan umumnya output dari Delta-Sigma Modulator berupa sinyal digital 1 bit. Output dari Delta-Sigma Modulator disebut juga *pulse density modulation* karena densitas nilai high pada output menyimpan informasi sinyal input analog. Delta-Sigma Modulator sangat umum digunakan sebagai analog to digital converter dengan menambahkan *lowpass filter* digital pada output dari modulator. Delta-Sigma ADC mempunyai resolusi yang lebih tinggi dibanding dengan jenis ADC lainnya. Resolusi dari Delta-Sigma modulator ditentukan oleh *oversampling ratio*, semakin tinggi resolusi dari modulator, akan tetapi *bandwidth* sinyal akan menjadi semakin rendah.

Pada skripsi ini sebuah Delta-Sigma Modulator akan disimulasikan dengan topologi rangkaian second-order. *Oversampling ratio* yang dipilih untuk simulasi adalah 64. O*versampling ratio* yang tinggi akan membuat simulasi menjadi terlalu lama dan memerlukan banyak memori RAM. Oleh karena itu *oversampling ratio* 64 dipilih karena pertimbangan tersebut. Rangkaian second-order modulator akan dicoba disimulasikan dalam bentuk integrated circuit. Oleh karena itu layout *integrated circuit* dari modulator akan dibuat dengan menggunakan program Electric VLSI. Pertama – tama rangkaian dari second-order modulator dibuat dengan menggunakan program Electric VLSI dengan menggunakan model transistor BSIM4 50 nm. Setelah itu layout dari modulator dibuat dengan program yang sama dengan menggunakan *design rule* MOSIS SCMOS deepsubmicron. Kemudian layout yang telah dibuat dicek apakah sama dengan *schematic* rangkaian dengan fungsi LVS (*Layout versus Schematic*) yang ada di program

Electric VLSI. Layout second-order modulator telah dibuat dengan luas area 65 x 21 μm dengan jumlah transistor 208 buah.

Layout yang sudah dibuat kemudian disimulasikan dengan menggunakan LTSpice dan Winspice. Program LTSpice digunakan untuk menghasilkan grafik – grafik output dan input dari modulator sedangkan program Winspice digunakan untuk menghitung SNR dari modulator. Hasil simulasi program LTSpice pada bab 4 menunjukkan bahwa modulator telah bekerja dengan baik. Dari Gambar 4.33 terlihat output modulator merupakan sinyal digital 1 bit dengan densitas pulsa highnya berisi informasi sinyal input. Kemudian pada Gambar 4.36 terlihat fungsi modulator sebagai ADC. Output modulator yang digital jika dilewatkan pada *lowpass filter* analog akan berubah mendekati sinyal input analog. Kemudian, simulasi dengan menggunakan Winspice dengan nilai kapasitor C1,C2 0,3 pf menghasilkan nilai SNR sebesar 54,01 dB. Pada ADC, nilai SNR dapat dihubungkan dengan bit efektif dari suatu ADC. Oleh karena itu, resolusi modulator dapat diketahui dari nilai SNRnya yaitu sebesar 10 bit.

Kemudian optimasi lebih lanjut dilakukan dengan mengubah – ubah nilai kapasitor C1,C2 untuk mendapatkan SNR yang lebih tinggi. Hasilnya, SNR lebih tinggi didapatkan ketika nilai kapasitor C1,C2 0,2 pf. Karena kapasitor pada *integrated circuit* mempunyai kapasitansi parasitik antara layer poly1 dan substrat, maka optimasi selanjutnya dilakukan dengan mengubah – ubah nilai kapasitansi parasitik dengan mengubah ukuran poly1 untuk mengetahui efek perubahan kapasitansi parasitik terhadap nilai SNR modulator. Ternyata ketika nilai kapasitansi parasitik 1ff, nilai SNR naik dengan jauh menjadi 93,08 dB. Dengan nilai SNR tersebut didapatkan resolusi modulator sebesar 15 bit.

### **DAFTAR REFERENSI**

- [1] Baker, R. Jacob. (2002). *CMOS : Mixed Signal Circuit Design* (1<sup>st</sup> edition). United States of America : Wiley-IEEE Press.

- [2] CMOS Wikipedia. Diakses pada 6 Juni 2011. http://en.wikipedia.org/wiki/CMOS

- [3] Electric Wikipedia. Diakses pada 6 Juni 2011. http://en.wikipedia.org/wiki/Electric\_(software)

- [4] Delta Sigma Modulation Wikipedia. Diakses pada 28 Mei 2011. http://en.wikipedia.org/wiki/Delta-sigma\_modulation

- [5] 1-bit A/D and D/A Converters. Diakses pada 28 Mei 2011. http://www.cs.tut.fi/sgn/arg/rosti/1-bit/

- [6] Baker, R. Jacob. (2005). *CMOS*: Circuit Design, Layout and Simulation (3<sup>rd</sup> edition). United States of America: Wiley-IEEE Press.

- [7] Design Rules MOSIS Scalable CMOS (SCMOS) (Revision 8.00). Diakses pada 7 Juni 2011.

- http://www.mosis.com/Technical/Designrules/scmos/scmos-main.html

### **DAFTAR PUSTAKA**

Schreier, Richard, & Temes, Gabor C. (2004). *Understanding Delta-Sigma Data Converters*. United States of America: Wiley-IEEE Press.

LTSpice video tutorials from CMOSedu.com. Diakses pada 30 Desember 2010. http://cmosedu.com/videos/ltspice/ltspice videos.htm

Electric VLSI Tutorials from CMOSedu.com. http://cmosedu.com/videos/electric/electric videos.htm

Nuryadi. (2010). Optimasi Differensial Operasional Amplifier CMFB dengan VDD 1 volt dan Slew Rate 1500 mV/nS. Depok: Fakultas Teknik Universitas Indonesia.