#### ANALISIS PERBANDINGAN ANTARA SYNCHRONOUS ETHERNET DENGAN IEEE 1588 V2 SEBAGAI TEKNOLOGI SINKRONISASI NEXT GENERATION

#### **SKRIPSI**

## **BAYU PRATAMA 0806455124**

## FAKULTAS TEKNIK PROGRAM STUDI TEKNIK ELEKTRO DEPOK JULI 2012

#### ANALISIS PERBANDINGAN ANTARA SYNCHRONOUS ETHERNET DENGAN IEEE 1588 V2 SEBAGAI TEKNOLOGI SINKRONISASI NEXT GENERATION

#### **SKRIPSI**

Diajukan sebagai salah satu syarat untuk memperoleh gelar Sarjana Teknik

#### BAYU PRATAMA 0806455124

# FAKULTAS TEKNIK PROGRAM STUDI TEKNIK ELEKTRO KEKHUSUSAN TELEKOMUNIKASI DEPOK JULI 2012

#### HALAMAN PERNYATAAN ORISINALITAS

Skripsi ini adalah hasil karya saya sendiri, dan semua sumber baik yang dikutip maupun dirujuk telah saya nyatakan dengan benar.

Nama : Bayu Pratama

NPM : 0806455124

Tanda Tangan :....

Tanggal : 2 Juli 2012

#### **HALAMAN PENGESAHAN**

Skripsi ini diajukan oleh :

Nama : Bayu Pratama NPM : 0806455124 Program Studi : Teknik Elektro

Judul Skripsi : Analisa Perbandingan Antara Synchronous

Ethernet Dengan IEEE 1588 v2 sebagai Teknologi Sinkronisasi Next Generation

Telah berhasil dipertahankan di hadapan Dewan Penguji dan diterima sebagai bagian persyaratan yang diperlukan untuk memperoleh gelar Sarjana Teknik pada Program Studi Teknik Elektro Fakultas Teknik Universitas Indonesia

#### **DEWAN PENGUJI**

Perabimbing : Ir Arifin Djauhari, MT

Penguji : Dr. Fitri Yuli Zulkifli S.T., M.Sc.

Penguji : Basari ST. MEng. PhD

Ditetapkan di: Depok

Tanggal : 2 Juli 2012

#### KATA PENGANTAR

Puji syukur saya panjatkan kepada Tuhan Yang Maha Esa, karena atas berkat dan rahmat-Nya, saya dapat menyelesaikan Skripsi ini. Penulisan Skripsi ini dilakukan dalam rangka memenuhi salah satu syarat untuk mencapai gelar Sarjana Teknik Jurusan Teknik Elektro pada Fakultas Teknik Elektro Universitas Indonesia. Saya menyadari bahwa, tanpa bantuan dan bimbingan dari berbagai pihak, dari masa perkuliahan sampai pada penyusunan Skripsi ini, sangatlah sulit bagi saya untuk menyelesaikan Skrispsi ini. Oleh Karena itu saya mengucapkan terima kasih kepada:

- (1) Bpk Ir.Arifin Djauhari, MT. Selaku dosen pembimbing yang telah menyediakan banyak waktu, tenaga dan pikiran untuk mengarahkan saya dalam penyusunan Skripsi ini;

- (2) Ibu Dr. Fitri Yuli Zulkifli S.T., M.Sc.selaku dosen penguji yang telah memberikan masukan kontributif dalam sidang skripsi;

- (3) Bapak Basari ST. MEng. PhD selaku dosen penguji yang telah memberikan masukan kontributif dalam sidang skripsi;

- (4) PT. Telkom Indonesia Tbk yang banyak membantu dalam usaha memperoleh data yang saya perlukan.

- (5) Bapak Hikmatullah Insan Purnama, Bapak Muhlis Mustaming, Bpk Didi Jajat Sejati dan Bpk Kurnendi yang telah memberikan pengetahuan serta masukan kontributif dalam penulisan buku skripsi.

- (6) Orang tua dan keluarga saya yang telah memberikan bantuan berupa dukungan moral dan material; dan

- (7) Para Sahabat yang telah membantu saya dalam menyelesaikan Skripsi ini.

Akhir kata, saya berharap Tuhan Yang Maha Esa berkenan membalas segala kebaikan semua pihak yang telah membantu. Semoga Skripsi ini membawa manfaat bagi pengembangan ilmu pengetahuan.

Depok, 2 Juli 2012

Bull

Penulis

## HALAMAN PERNYATAAN PERSETUJUAN PUBLIKASI TUGAS AKHIR UNTUK KEPENTINGAN AKADEMIS

Sebagai sivitas akademik Universitas Indonesia, saya yang bertanda tangan di bawah ini:

Nama : Bayu Pratama

NPM : 0806455124

Program Studi : Teknik Elektro

Departemen : Teknik Elektro

Fakultas : Teknik

Jenis Karya : Skripsi

Demi pengembangan ilmu pengetahuan, menyetujui untuk memberikan kepada Universitas Indonesia Hak Bebas Royalti Noneksklusif (*Non-exclusive Royalty-Free Right*) atas karya ilmiah saya yang berjudul:

#### ANALISA PERBANDINGAN ANTARA SYNCHRONOUS ETHERNET DENGAN IEEE 1588 V2 SEBAGAI TEKNOLOGI SINKRONISASI NEXT GENERATION

Beserta perangkat yang ada (jika diperlukan). Dengan Hak Bebas Royalti Noneksklusif ini Universitas Indonesia berhak menyimpan, mengalihmedia/formatkan, mengelola dalam bentuk pangkalan data (*database*), merawat, dan memublikasikan tugas akhir saya selama tetap mencantumkan nama saya sebagai penulis/pencipta dan sebagai pemilik Hak Cipta.

Demikian pernyataan ini saya buat dengan sebenarnya.

Dibuat di : Depok

Pada tanggal: 2 Juli 2012

Yang menyatakan

(Bayu Pratama)

#### **ABSTRAK**

Nama : Bayu Pratama Program Studi : Teknik Elektro

Judul : Analisa Perbandingan Antara Synchronous Ethernet Dengan

IEEE 1588 v2 sebagai teknologi sinkronisasi Next Generation

Sinkronisasi merupakan suatu proses penyerempakan *clock* antara *transmitter* dengan *receiver* sehingga memiliki *timing* dan urutan yang sesuai dengan kondisi idealnya. Hal ini bertujuan untuk meminimalisir slip akibat perbedaan clock yang terjadi. Beberapa tahun mendatang teknologi SONET/SDH akan segera diperbaharui dengan teknologi Ethernet yang menawarkan berbagai fitur menarik dari segi layanan hingga pemanfaatan alokasi *Bandwidth*. Demi menjaga kualitas layanan, diperlukan penyerempakkan *clock* dengan mengedepankan teknologi terbaharui seperti *Synchronous Ethernet* (SyncE) dan IEEE 1588 v2 sebagai teknologi sinkronisasi *clock* masa depan.

Dalam skripsi ini, diberikan pembahasan mengenai perbandingan antara teknologi *Synchronous Ethernet* (SyncE) dengan IEEE 1588 v2 bedasarkan enam buah parameter teknis seperti *Timing support*, Kontinuitas pada Jalur *timing*, Jumlah *node* pada jalur sinkronisasi *timing*, akurasi frekuensi, konsep sinkronisasi, dan kompabilitas terhadap jaringan 4G. Dan memberikan solusi mengenai rancangan optimalisasi jaringan sinkronisasi masa depan dengan menerapkan kedua teknologi tersebut. Rancangan ini memberikan konsep dalam hal meminimalisir efek *Packet Delay Variation* (PDV), Efisiensi Bandwidth dan hasil akurasi Frekuensi yang cenderung stabil.

Dari hasil analisis perbandingan dari kedua teknologi tersebut, dapat ditarik kesimpulan bahwa teknologi IEEE 1588v2 memberikan sebuah performansi yang baik dan sangat cocok diimplementasikan ke dalam jaringan masa depan. Demi mengoptimalkan kinerja sinkronisasi *clock* untuk masa depan dapat menerapkan konsep penggabungan dari kedua teknologi tersebut. Karena dengan menggabungkan kedua teknologi tersebut, diharapkan dapat mampu mengatasi serta meminimalisir adanya efek *Packet Delay Variation* (PDV), Efisiensi Bandwidth dan hasil akurasi frekuensi yang cenderung stabil sehingga tingkat kualitas dari suatu layanan berbasis paket dapat dikatagorikan memiliki sinkronisasi *clock* terbaik.

Kata Kunci:

Sinkronisasi clock, Synchronous Ethernet, IEEE 1588v2

#### **ABSTRACT**

Nama : Bayu Pratama

Program Studi: Electrical Engineering

Judul : Analysis of Comparison Between Synchronous Ethernet and

IEEE 1588 v2 as synchronization technology Next Generation

Synchronization is a process of clock synchronization between transmitter and receiver that has the timing and sequence corresponding to the ideal conditions. It aims to minimize the occurence of slip due to the difference in clock. In a next few years, SONET / SDH technology will be updated with Ethernet technology which offers a variety of services features to the utilization of bandwidth allocation. In order to maintain the quality of service, that required clock synchronization by prioritizing renewable technologies such as Synchronous Ethernet (SyncE) and IEEE 1588 v2 as clock synchronization Next-Generations technologies.

In this Paper, given the discussion about the comparison between technologies Synchronous Ethernet (SyncE) and IEEE 1588 v2 based on six technical parameters such as timing support, continuity on the line timing, number of nodes on the path timing synchronization, frequency accuracy, the concept of synchronization, and compatibility of the network 4G. And offers a solution with the optimization design of future network synchronization by applying both technologies. This design gives the concept of to minimize Packet Delay Variation (PDV) effects, Bandwidth Efficiency, and stable Frequency.

As the results of a comparative analysis of both technologies, it can be concluded that the technology is IEEE 1588v2 give a best performance and suitable to be implemented into Next Generation Network. In order to optimize the performance of clock synchronization for the future can apply the concept of mergin the two technologies. Because by combining both technologies, is expected to be able to minimize Packet Delay Variation (PDV) effects, Bandwidth Efficiency and stable frequency so that the quality level of a packet-based services can be categorized to have the best clock synchronization.

Keywords:

Clock Synchronization, Synchronous Ethernet, IEEE 1588v2

#### **DAFTAR ISI**

| HAl        | LAMAN PERNYATAAN ORISINALITAS            | iii    |

|------------|------------------------------------------|--------|

| HAI        | LAMAN PENGESAHAN                         | iv     |

| KA         | ΓA PENGANTAR                             | V      |

| HAl        | LAMAN PERNYATAAN PERSETUJUAN PUBLIKASI   | vii    |

| TUC        | GAS AKHIR UNTUK KEPENTINGAN AKADEMIS     | vii    |

|            | STRAK                                    |        |

| ABS        | STRACT                                   | ix     |

|            | FTAR ISI                                 |        |

|            | FTAR GAMBAR                              |        |

|            | FTAR TABEL                               |        |

|            | FTAR SINGKATAN                           |        |

|            | FTAR ISTILAH/SIMBOL                      |        |

|            | FTAR PERSAMAAN                           |        |

| BAI        | B 1 PENDAHULUAN                          | 1      |

| 1.1<br>1.2 | Latar BelakangTujuan                     |        |

| 1.3<br>1.4 | Batasan Masalah                          |        |

| BAI        | B 2 SINKRONISASI JARINGAN TELEKOMUNIKASI | 5      |

| 2.1        | Sinkronisasi                             | 5<br>5 |

|            | · · ·                                    |        |

|       | 2.1.2 Parameter-Parameter Dasar Sinkronisasi                            |      |

|-------|-------------------------------------------------------------------------|------|

|       | 2.1.2.1 Akurasi Frekuensi                                               | 8    |

|       | 2.1.2.2 Kestabilan Frekuensi                                            | 8    |

|       | 2.1.2.3 Jitter dan Wander                                               |      |

|       | 2.1.2.4 TIE (Time Interval Error)                                       | 9    |

|       | 2.1.2.5 Packet Jitter/Packet Delay                                      | 9    |

|       | 2.1.3 Sinkronisasi Jaringan                                             | 9    |

|       | 2.1.4 Sinkronisasi Antar Jaringan                                       | . 12 |

| 2.2   | Teknologi Sinkronisasi Masa Depan                                       | . 13 |

| BAI   | 3 3 SYNCHRONOUS ETHERNET DAN IEEE 1588v2                                | . 15 |

|       |                                                                         |      |

| 3.1   | Synchronous Ethernet                                                    | . 15 |

|       | 3.1.1 Konsep Dasar Synchronous Ethernet                                 |      |

|       | 3.1.1.1 Konsep Distribusi <i>Clock</i> Pada <i>Synchronous Ethernet</i> | . 16 |

|       | 3.1.2 Implementasi <i>Synchronous Ethernet</i> (SyncE) pada Jaringan    | 1.5  |

| 2 2   | Telekomunikasi                                                          |      |

| 3.2   | IEEE 1588 v2                                                            | . 19 |

|       | 3.2.1 Konsep Dasar IEEE 1588v2                                          |      |

|       | 3.2.1.1 Two-Way Time Transfer (TWTT)                                    |      |

| 1     | 3.2.1.2 Konsep <i>Timing over Packet</i> (ToP)                          |      |

|       | 3.2.2 Implementasi IEEE 1588v2 pada Jaringan Telekomunikasi             | . 24 |

| RAI   | 3 4 ANALISIS PERBANDINGAN ANTARA SYNCHRONOUS                            |      |

|       | HERNET DENGAN IEEE 1588 V2                                              | . 27 |

|       |                                                                         |      |

| 4.1   | Tabel Perbandingan antara Synchronous Ethernet dengan IEEE 1588 v2      | 2.7  |

| 4.2   | Analisa Perbandingan <i>Synchronous Ethernet</i> dengan IEEE 1588 v2    |      |

|       | 4.2.1 Timing Support                                                    |      |

|       | 4.2.2 Kontinuitas pada jalur <i>timing</i>                              | 29   |

|       | 4.2.3 Jumlah <i>node</i> pada jalur sinkronisasi <i>timing</i>          |      |

|       | 4.2.4 Akurasi Frekuensi                                                 |      |

|       | 4.2.5 Konsep Sinkronisasi                                               |      |

|       | 4.2.6 Kompabilitas terhadap Teknologi 4G                                |      |

| 4.3   | Optimalisasi Penggunaan Synchronous Ethernet dan IEEE 1588v2 Dalam      |      |

|       | lementasi Jaringan Telekomunikasi                                       |      |

| BAI   | 3 5 KESIMPULAN                                                          | . 27 |

| DAI   | FTAR ACUAN                                                              | . 41 |

|       |                                                                         |      |

| 1 A T | TTAD DIICTAIZA                                                          | 11   |

#### DAFTAR GAMBAR

| Gambar 2.1 Clock di sisi Transmitter dan Receiver [2]                                             |

|---------------------------------------------------------------------------------------------------|

| Gambar 2.2 Proses <i>Clock Recovery</i> [2]6                                                      |

| Gambar 2.3 Data Buffering[2]                                                                      |

| Gambar 2.4 Hubungan antara kestabilan dengan akurasi frekuensi [3]                                |

| Gambar 2.5 Range frekuensi dari Jitter dan Wander [5]                                             |

| Gambar 2.6 Perbedaan fasa antara sinyal dengan sinyal acuan [3]                                   |

| Gambar 2.7 Konsep Hirarki Jaringan Sikronisasi dengan menerapkan konsep <i>Master-Slave</i> [6]   |

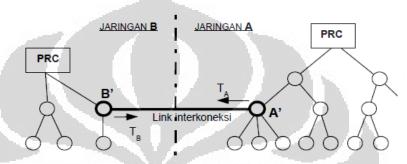

| Gambar 2.8 Sinkronisasi jaringan B dengan jaringan A [4]                                          |

| Gambar 2.9 Sinkronisasi antar jaringan dengan acuan PRC [4]                                       |

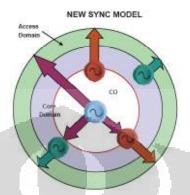

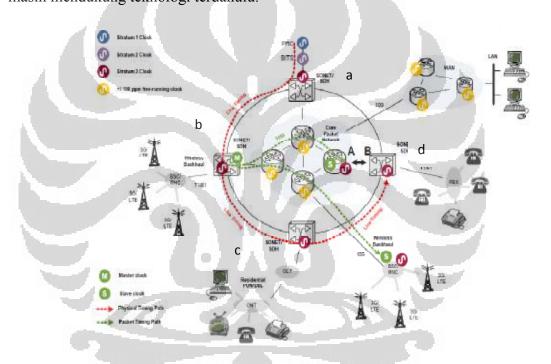

| Gambar 2.10 Model Sinkronisasi Next Generation [10]                                               |

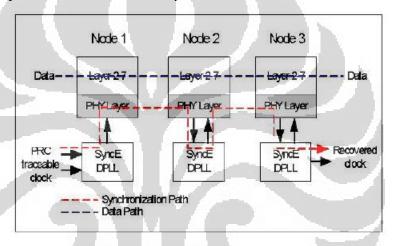

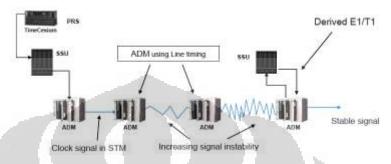

| Gambar 3.1 Konsep distribusi <i>clock</i> pada <i>Synchronous Ethernet</i> [1] 16                 |

| Gambar 3.2 Distribusi Frekuensi Sinkronisasi dengan Implementasi <i>Synchronous Ethernet</i> [11] |

| Gambar 3.3 Distribusi Frekuensi Pada Synchronous Ethernet [10]                                    |

| Gambar 3.4 Distribusi Frekuensi pada SONET/SDH [10]                                               |

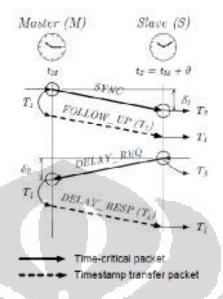

| Gambar 3.5 Konsep Two-Way Time Transfer (TWTT) pada IEEE 1588 v2 [12] 21                          |

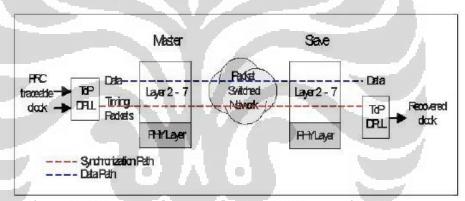

| Gambar 3.6 Konsep <i>Timing over Packet</i> (ToP) [1]                                             |

| Gambar 3.7 Distribusi <i>Timing</i> Berbasis Paket [11]25                                         |

| Gambar 4.1 Distribusi sinkronisasi pada PHY Ethernet. [11]                                        |

| Gambar 4.2 IEEE 1588 v2 Boundary Clock [17]                                           | 30 |

|---------------------------------------------------------------------------------------|----|

| Gambar 4.3 Kombinasi antara <i>Synchronus Ethernet</i> (SyncE) dengan IEEE 158 v2 [1] |    |

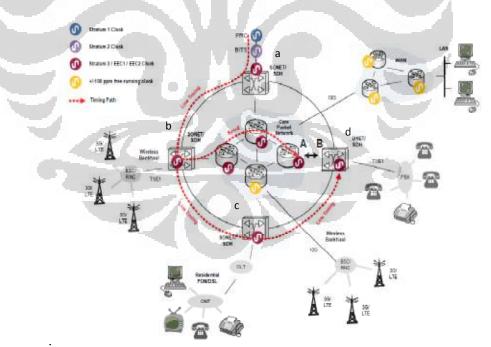

| Gambar 4.4 Gambar Rancangan Optimalisasi Sinkronisasi Jaringan Telekomunikasi.        | 37 |

#### DAFTAR TABEL

| Tabel 2.1. ANSI T1.101 Stratum Clock Level Requirements [8]    | 11 |

|----------------------------------------------------------------|----|

| Tabel 4.1 Tabel perbandingan antara Synchronous Ethernet denga |    |

#### **DAFTAR SINGKATAN**

PRC : Primary Reference Clock

SyncE : Synchronous Ethernet

PTP : Precise Time Protocol

NTP : Network Time Protocol

TWTT : Two Way Time Transfer

DSN : Digital Switching Network

VCO : Voltage Controlled Oscillator

PLL : Phased Locked Loop

DPLL : Digital Phased Locked Loop

TDM : Time Division Multiplexing

SONET/SDH : Synchronous Digital Hierarchy

QoS : Quality of Service

NGN : Next Generation Network

ToD : Time of Day

EEC : Ethernet Equipment Clock ADM : Add and Drop Multiplexer

ToP: Timing over Packet

PDV: Packet Delay Variation

MSC: Message Switching Centre

SLA: Service Level Agreement

GPS: Global Positioning System

LTE : Long Term Evolution

SSU : Synchronization Supply Unit

4G : Fourth Generation

#### DAFTAR ISTILAH/SIMBOL

#### **Daftar Simbol**

Θ : Time Critical packet

$\Theta_{\text{error}}$ : *Error* karena ketidaksimetrisan *Delay*

#### **Daftar Istilah**

*Clock* : Alat yang memberikan sinyal *timing*

(pewaktu) [4].

Sinyal *Timing* : Sinyal yang siklis (periodik) untuk

mengendalikan suatu operasi[4].

Jitter : Variasi dalam jangka pendek yang tidak

kumulatif saat (instant) signifikan suatu sinyal dijital dari posisinya yang ideal pada

skala waktu[4].

Wander : Variasi dalam jangka panjang yang tidak

kumulatif saat (instant) signifikan suatu sinyal dijital dari posisinya yang ideal pada

skala waktu[4].

Jaringan Sinkronisasi : Rangkaian simpul dan *link* sinkronisasi

yang berfungsi untuk mensikronisasikan *clock* di, atau disambungkan kepada

simpul-simpul tersebut [4].

#### DAFTAR PERSAMAAN

| (3.1) | 21 |

|-------|----|

| (3.2) | 21 |

| (3.3) | 21 |

#### BAB 1 PENDAHULUAN

#### 1.1 Latar Belakang

Dewasa ini, bidang telekomunikasi adalah salah satu bidang yang memegang peranan penting dalam pertumbuhan ekonomi di seluruh belahan dunia. Dimana dengan adanya telekomunikasi, semua orang di belahan dunia bisa saling bertukar informasi dalam bentuk data, *video*, maupun suara. Seiring dengan meningkatnya jumlah populasi manusia dan perkembangan zaman dalam bidang teknologi, secara otomatis akan memperbesar minat konsumen untuk mengakses data yang membutuhkan *bandwidth* yang besar dengan beberapa pilihan layanan yang sangat bervariasi dengan menunjang kualitas layanan yang baik dengan koneksi kecepatan yang cepat, dan harga yang murah. Hal inilah yang mendorong *provider* atau penyedia layanan untuk mengembangkan teknologi yang sudah ada menjadi teknologi masa depan atau yang dikenal dengan teknologi *Next-Generation*. Hal ini berdampak secara langsung maupun tidak langsung dalam perkembangan jaringan telekomunikasi dunia maupun di Indonesia.

Teknologi *Next-Generation* itu sendiri merupakan suatu era ataupun proses migrasi dari teknologi sebelumnya yakni teknologi TDM menuju teknologi berbasis paket. Tantangan terbesar dari teknologi *Next-Generation* itu sendiri menuntut *provider* untuk memberikan layanan yang berkualitas dan menjanjikan, menekan dan meminimalisir biaya yang keluar dalam menyediakan sebuah layanan, dan juga meningkatkan pendapatan dari layanan yang disediakan. Untuk itu penyedia layanan kini telah berpindah dari yang semula melayani layanan suara kini beralih ke layanan jaringan paket sebagai solusi dari permasalahan yang mereka hadapi. Atas dasar untuk memenuhi proses berlangsungnya suatu pembicaraan atau komunikasi diperlukan adanya konsep sinkronisasi.

Beberapa tahun mendatang teknologi SONET/SDH akan segera diperbaharui dengan teknologi Ethernet yang menawarkan berbagai fitur menarik dari segi layanan hingga pemanfaatan alokasi *Bandwidth* . Maka dari itu proses sinkronisasi sangatlah diperlukan untuk menunjang adanya perbaikan kualitas layanan. Sinkronisasi itu sendiri adalah sebuah proses penyerempakan *clock*

antara *transmitter* dengan *receiver* sehingga memiliki *timing* dan urutan yang sesuai dengan kondisi idealnya. Tujuan dari penyerempakan *clock* itu sendiri adalah untuk meminimalisir maupun mengeliminasi terjadinya *slip* yang disebabkan oleh adanya perbedaan *clock* yang dibangkitkan oleh sumber *clock*. Dengan mengedepankan teknologi terbaharui seperti *Synchronous Ethernet* (SyncE) dan IEEE 1588 v2 diharapkan mampu sebagai teknologi sinkronisasi *clock* masa depan.

Berkembanganya sebuah jaringan sinkronisasi menuntut adanya suatu terobosan terbaru dalam hal sinkronisasi *clock* masa depan. Dengan memberikan sebuah analisis perbandingan antara teknologi *Synchronous Ethernet* (SyncE) dengan IEEE 1588v2 dari penelitian yang sebelumnya telah ada akan memberikan sebuah masukan yang kontributif dalam pemilihan teknologi sinkronisasi *clock* [1]. Selain itu, dengan memberikan sebuah rancangan optimalisasi jaringan sinkronisasi *clock* masa depan dengan menggabungkan kedua teknologi tersebut, diharapkan memberikan suatu pemecahan masalah terhadap alokasi bandwidth hingga permasalahan efek *Packet Delay Variation* (PDV). Atas dasar ini, dengan memberikan sebuah ilustrasi mengenai sinkronisasi masa depan diharapkan memberikan sebuah kontribusi serta inovasi dalam menangangi permasalahan sinkronisasi *clock* untuk jaringan *Next-Generation* yang mengedepankan sinkronisasi dalam jaringan berbasis paket

Dalam skripsi ini, akan diberikan pembahasan mengenai perbandingan antara teknologi *Synchronous Ethernet* (SyncE) dengan IEEE 1588 v2 dilihat bedasarkan enam buah parameter-parameter teknis seperti *Timing support*, Kontinuitas pada Jalur *timing*, Jumlah *node* pada jalur sinkronisasi *timing*, akurasi frekuensi, konsep sinkronisasi, dan kompabilitas terhadap jaringan 4G serta memberikan sebuah solusi mengenai rancangan optimalisasi terhadap jaringan sinkronisasi masa depan dengan menerapkan teknologi *Synchronous Ethernet* (SyncE) dengan IEEE 1588 v2 yang didasari berdasarkan enam paramater-paramter teknis tersebut sehingga dapat memberikan sebuah penawaran konsep dalam hal meminimalisir efek *Packet Delay Variation* (PDV), Efisiensi Bandwidth dan hasil akurasi sinkronisasi frekuensi yang cenderung stabil.

#### 1.2 Tujuan

Tujuan dari Skripsi ini adalah melakukan analisis perbandingan antara Synchronous Ethernet dengan IEEE 1588 v2 dengan pendekatan parameter-parameter teknis yang terdapat di dalam kedua teknologi tersebut.

#### 1.3 Batasan Masalah

Adapun batasan masalah pada skripsi adalah membatasi permasalahan ke arah analisis perbandingan antara *Synchronous Ethernet* dengan IEEE 1588 v2 berdasarkan parameter teknis seperti *timing support*, kontinuitas pada jalur *timing*, jumlah *node* pada jalur sinkronisasi *timing*, akurasi frekuensi, konsep sinkronisasi, dan kompabilitas/ mendukung teknologi 4G. Dan memberikan penilaian dari parameter teknis tersebut serta memberikan konsep rancangan optimalisasi untuk mendapatkan akurasi frekuensi yang stabil, meminimalisir efek *Packet Delay Variation* (PDV), dan efisiensi *Bandwidth*.

#### 1.4 Sistematika Penulisan

Skripsi ini disajikan dengan sistematika penulisan sebagai berikut:

#### • BAB I PENDAHULUAN

Bab ini menguraikan tentang latar belakang masalah, tujuan penulisan, batasan masalah, serta sistematika skripsi.

#### • BAB II SINKRONISASI JARINGAN TELEKOMUNIKASI

Bab ini berisi penjelasan mengenai konsep dasar sinkronisasi yang diterapkan pada jaringan telekomunikasi dan memaparkan konsep-konsep dalam penyerempakan *clock* secara umum

#### • BAB III SYNCHRONOUS ETHERNET DAN IEEE 1588 V2

Bab ini memberikan penjelasan mengenai konsep dasar dan beberapa pengetahuan umum mengenai teknologi Synchronous Ethernet dan IEEE 1588v2 dengan mengklasifikasikannya dalam beberapa parameter teknis.

### • BAB IV ANALISIS PERBANDINGAN ANTARA SYNCHRONOUS ETHERNET DENGAN IEEE 1588 V2

Bab ini memberikan analisis mengenai perbandingan antara *Synchronous Ethernet* (SyncE) dengan IEEE 1588 v2 dengan beberapa parameter-parameter teknis yang telah dibahas pada bab III.

#### • BAB V KESIMPULAN

Bab ini berisikan mengenai penjelasan tentang kesimpulan yang dapat diambil dari beberapa penjelasan sebelumnya dan dapat diambil intisari berupa saran mengenai teknologi yang cocok dipakai di Indonesia.

#### BAB 2

#### SINKRONISASI JARINGAN TELEKOMUNIKASI

#### 2.1 Sinkronisasi

Dewasa ini, seiring dengan meningkatnya tingkat kebutuhan manusia akan informasi membuat pihak *provider* berlomba-lomba menyediakan berbagai fasilitas layanan dengan kualitas yang terbaik. Oleh karena itu, suatu jaringan dijital harus dioperasikan secara serempak. Terlebih lagi, jika layanan yang akan digunakan berupa layanan multimedia yang mencakup suara (*audio*), *data*, dan *video* (gambar) yang diperuntukkan untuk publik. Untuk itu diperlukan adanya sinkronisasi *clock* pada jaringan telekomunikasi.

Secara umum, sinkronisasi merupakan suatu proses penyerempakan *clock* antara *transmitter* dengan *receiver* sehingga memiliki *timing* dan urutan yang sesuai dengan kondisi idealnya. Tujuan dari penyerempakan *clock* itu sendiri adalah untuk meminimalisir maupun mengeliminasi terjadinya *slip* yang disebabkan oleh adanya perbedaan *clock* hasil sinkronisasi dengan *clock* awal yang dibangkitkan oleh *Primary Reference Clock* (PRC).

#### 2.1.1 Konsep Dasar Sinkronisasi

Pada dasarnya konsep sinkronisasi harus memiliki keterkaitan dengan melihat dari dua sudut pandang yang berbeda yakni dilihat dari sisi *transmitter* dan *receiver* dengan menerapkan konsep rangkaian *Phase Locked Loop* (PLL) di dalamnya.

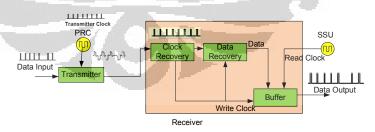

Gambar 2.1 *Clock* di sisi *Transmitter* dan *Receiver* [2]

Pada gambar 2.1 menunjukkan bahwa mula-mula sinyal *input* yang diterima oleh *transmitter* terdiri atas *data input* yang kemudian akan diberikan asupan sinyal *clock* dari *Primary Reference Clock* (PRC). Sehingga, sinyal tersebut mengandung *data* dan *clock*. Kemudian sinyal tersebut ditransmisikan melalui jalur transmisi hingga sampai ke sisi *receiver*.

Informasi yang terkandung dalam sinyal tersebut tidaklah utuh sepenuhnya diterima oleh *receiver*. Hal ini dikarenakan adanya gangguangangguan selama proses transmisi berlangsung. Untuk menjaga agar isi informasi yang disampaikan tetap utuh dan serempak, maka diperlukan adanya pemulihan *clock* dan pencocokan kembali dari *timing clock* tersebut agar sesuai dengan kondisi semula.

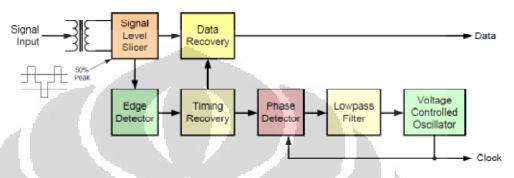

Gambar 2.2 Proses Clock Recovery [2]

Gambar 2.2 menunjukkan ilustrasi pemisahan *clock* dengan *data*. Mulamula sinyal hasil keluaran dari *transmitter* diproses terlebih dahulu oleh *Signal level Slicer* untuk dipisahkan antara *data* dengan *clock*. Setelah dipisahkan, *data* akan langsung dibangkitkan kembali oleh *Data Recovery*. Sedangkan *clock* harus disinkronkan kembali dengan *data*. *Clock* hasil *Signal Level Slicer* akan diteruskan ke *edge detector* untuk dilihat posisi serta *timing clock* tersebut. Kemudian *timing data* dan *clock* akan diserempakan kembali oleh *Timing Recovery*.

Clock kemudian diteruskan ke dalam rangkaian Phase Locked Loop (PLL). Rangkaian Phase Locked Loop (PLL) terdiri atas Phase Detector, Low Pass Filter (LPF) dan Voltage Controlled Oscillator (VCO). Dimana hasil keluaran clock dari rangkaian Phase Locked Loop (PLL) akan digunakan sebagai write clock untuk proses Buffer. Setelah timing clock telah disesuaikan, clock diteruskan ke Phase Detector untuk dibandingkan sinyal clock tersebut dengan sinyal masukan awal. Apabila tidak sesuai, maka akan menghasilkan sinyal error yang proposional dengan perbedaan fasa yang terjadi diantara keduanya. Kemudian, sinyal error tersebut disaring oleh Low Pass Filter sehingga akan terlihat perbedaan fasa yang terjadi. Hal inilah yang akan memberikan peranan

Voltage Controlled Oscillator (VCO) untuk membentuk fasa keluaran yang terkunci oleh sistem *Phase Locked Loop* (PLL).

Apabila fasa keluaran mengalami penyimpangan atau *drift*, sinyal *error* akan meningkat sehingga mendorong fasa hasil *Voltage Controlled Oscillator* (VCO) akan beroperasi ke arah yang berlawanan demi mengurangi *error* tersebut. Bila kondisi ini tidak terpenuhi, maka fasa akan dikembalikan kembali ke rangkaian awal dari *Phase Locked Loop* (PLL). Sehingga proses ini dapat dikatakan sebagai proses umpan balik negatif.

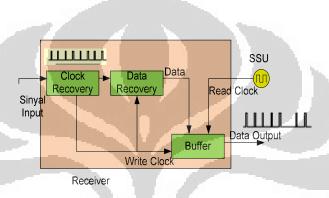

Gambar 2.3 Data Buffering[2]

Proses selanjutnya adalah proses *Buffer* yang akan diilustrasikan pada gambar 2.3. Proses ini akan menyatukan antara *data* hasil akhir *Data Recovery* dengan *clock* hasil keluaran dari rangkaian *Phase Locked Loop* (PLL). Dalam proses penyatuan ini akan menunjukkan perbedaan fasa ataupun frekuensi yang berarti, sehingga dibutuhkan sebuah catu *clock* tambahan yang diambil dari *Synchronization Supply Unit* (SSU) terdekat. Sehingga *clock* catu tambahan akan dipergunakan sebagai *Read Clock*. Proses penyatuan *read clock* dengan *write clock* pada *Buffer* sangat rentan terhadap *Jitter* dan *Wander* serta perbedaan frekuensi yang dihasilkan. Maka, untuk menghindari hal tersebut *clock* harus dibuat persis sama dengan *clock* awal.

#### 2.1.2 Parameter-Parameter Dasar Sinkronisasi

Dalam suatu jaringan telekomunikasi, apabila suatu layanan dapat dikatakan memenuhi kualitas terbaik, maka kerap dikaitkan oleh adanya proses penyerempakan *clock* selama proses tersebut tidak mengalami adanya *slip* maupun gangguan-gangguan yang terjadi selama proses pendistribusian *clock*. Untuk itulah, ada beberapa parameter-parameter dasar sinkronisasi yang perlu

diperhatikan agar memenuhi kualitas suatu layanan dapat tergolong dalam kualitas terbaik. Diantaranya adalah Akurasi Frekuensi, Kestabilan Frekuensi, *Jitter, Wander, Time Interval Error* (TIE) dan *Packet Jitter (Delay Variation)* [3].

#### 2.1.2.1 Akurasi Frekuensi

Suatu frekuensi dikatakan memiliki tingkat akurasi yang tinggi adalah dimana besaran deviasi antara posisi ideal dengan perubahan frekuensi yang terjadi sangat kecil. Hal ini sangat berkaitan langsung dengan penentuan serta kompabilitas suatu layanan. Dimana ada beberapa layanan yang masih membutuhkan adanya spesifikasi akurasi frekuensi untuk mendukung kompabilitas layanan tersebut yang akan diterapkan ke dalam konsep jaringan telekomunikasi masa depan atau *Next-Generation Network*.

#### 2.1.2.2 Kestabilan Frekuensi

Kestabilan frekuensi adalah kemampuan dari oscillator untuk menjaga agar frekuensi tetap dalam keadaan stabil dan tidak terpengaruh oleh kondisi apapun yang berasal dari lingkungan maupun dari tingkat keelektrikan.[3]

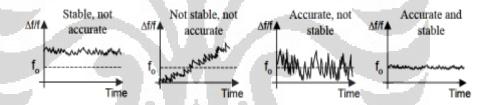

Gambar 2.4 Hubungan antara kestabilan dengan akurasi frekuensi [3]

Gambar 2.4 menunjukkan beberapa contoh keterkaitan antara tingkat akurasi frekuensi dengan kestabilan frekuensi. Dari gambar tersebut diharapkan frekuensi memiliki tingkatan keakuratan yang akurat dan stabil, hal itu dikaitkan dengan *Jitter* dan *Wander*. Karena dengan kondisi frekuensi yang akurat dan stabil akan memperkecil peluang terjadinya *Jitter* dan *Wander*.

#### 2.1.2.3 Jitter dan Wander

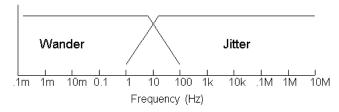

Jitter adalah suatu gejala yang terjadi saat adanya perbedaan fasa dengan frekuensi lebih besar 10 Hz atau dapat dikatakan pula Variasi dalam jangka pendek yang tidak kumulatif saat (instant) signifikan suatu sinyal dijital dari posisinya yang ideal pada skala waktu [4]. Sedangkan wander terjadi saat perbedaan fasa dengan frekuensi kurang dari 10 Hz. Atau Variasi dalam jangka panjang yang tidak kumulatif saat (instant) signifikan suatu sinyal dijital dari

posisinya yang ideal pada skala waktu [4]. Hal ini ditunjukkan oleh gambar 2.5 berdasarkan atas Rekomendasi ITU-T G.810.[5]

Gambar 2.5 Range frekuensi dari Jitter dan Wander [5]

#### 2.1.2.4 TIE (Time Interval Error)

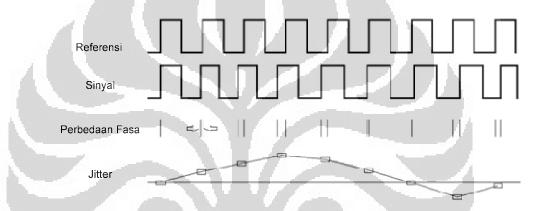

Time Interval Error (TIE) adalah suatu kondisi dimana adanya perbedaan fasa antara sinyal dengan *clock* acuan berdasarkan periode waktu tertentu [3].

Gambar 2.6 Perbedaan fasa antara sinyal dengan sinyal acuan [3]

Dengan adanya gambar 2.6 menunjukkan adanya keterkaitan *Time Interval Error* (TIE) dengan *Jitter* dimana terlihat bahwa dengan perbedaan fasa yang terjadi antara sinyal dengan referensi, maka akan menentukan besaran nilai *jitter* yang terjadi pada sinyal tersebut.

#### 2.1.2.5 *Packet Jitter/Packet Delay*

Packet Delay seringkali dikaitkan dnegan adanya perubahan delay yang terjadi antara satu paket timing dengan paket timing lainnya. Hal ini disebabkan adanya perubahan pola routing secara mendadak dan juga adanya delay antrian yang disebabkan bertambahnya beban traffic atau dapat dikatakan sebagai kongesi. Sehingga paket-paket tersebut harus menunggu dalam antrian tersebut hingga beban traffic mengalami penurunan.

#### 2.1.3 Sinkronisasi Jaringan

Sinkronisasi jaringan adalah proses penyerempakan *clock* yang berlangsung dalam sebuah jaringan yang membentuk jaringan sinkronisasi dengan

mengendalikan *clock* yang dibangkitkan oleh sumber *clock*. Jaringan-jaringan sinkronisasi apabila disatukan dan dikaitkan antara satu jaringan sinkronisasi dengan jaringan sinkronisasi lainnya akan membentuk sebuah jaringan yang besar, sehingga dapat dinamakan Jaringan Sinkronisasi Nasional. Untuk itulah, setiap penyelenggara jaringan harus bertanggung jawab secara penuh atas perangkat-perangkat yang berada di dalam jaringannya [4].

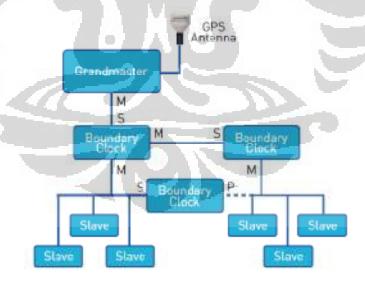

Gambar 2.7 Konsep Hirarki Jaringan Sikronisasi dengan menerapkan konsep *Master-Slave* [6]

Jaringan sinkronisasi akan membentuk sebuah konsep hirarki *Master-Slave* yang menggambarkan posisi kedudukan *Master node* lebih tinggi ketimbang *Slave node*. Hal ini diterapkan dimana *Primary Reference Clock* (PRC) sebagai perangkat yang berperan secara aktif dalam hal membangkitkan *clock* dengan akurasi sebesar 1x10<sup>-11</sup> [5] untuk didistribusikan hingga sampai ke *Network Element* (NE). Dan *Primary Reference Clock* (PRC) itu sendiri harus memenuhi spesifikasi lain yang telah disebutkan dalam Rekomendasi ITU-T G.811 [7].

Dalam perencanaan alur sinkronisasi suatu jaringan sinkronisasi perlu diperhatikan bahwa adanya jalur alternatif apabila selama proses penyerempakan clock mengalami gangguan. Secara konsep, bila dikatikan dengan gambar 2.7, jika pada Synchronization Supply Unit (SSU) mengalami kehilangan acuan atas sinkronisasi clock yang diterima dari Primary Reference Clock (PRC), maka Synchronization Supply Unit (SSU) akan mencari sumber Primary Reference Clock (PRC) cadangan yakni Global Positioning System (GPS) atau melakukan

#### Universitas Indonesia

sinkronisasi antar jaringan yang melibatkan jaringan lain yang memiliki *clock* acuan yang serupa dan terhubung melalui *Link* interkoneksi. Konsep ini dikenal dengan mode *holdover*, dan konsep ini akan berakhir ketika *clock* sekali lagi beroperasi dalam mode normal.

Berbeda halnya dengan *Network Element* (NE) yang memiliki kecenderungan, jika *Network Element* (NE) tersebut kehilangan catu acuan *clock* sinkronisasi, maka dengan mencari *clock Synchronization Supply Unit* (SSU) yang berada dekat dengan *Network Element* (NE) tersebut sehingga *clock* tidak akan kehilangan sinkronisasi dan tidak membutuhkan adanya interkoneksi ke jaringan sinkronisasi lain.

Stratum Pull in Range Stability Time to First Accuracy Adjusment Frame Slip Range  $1 \times 10^{-11}$ 1 (PRC) N/A N/A 72 Days  $1x10^{-10}/Day$ 1.6x10<sup>-8</sup> 2 (SSU) 7 Days Synchronizing Accuracy of  $+/-1.6x10^{-8}$  $4.6 \times 10^{-6}$  $4.6 \times 10^{-6}$  $1,2x10^{-8}/Day$ 3E (NE) 7 Hours  $4.6 \times 10^{-6}$  $3.7 \times 10^{-7} / Day$ -3 6 Minutes Synchronizing Accuracy of  $+/-4.6 \times 10^{-6}$  $32x10^{-6}$ Synchronizing 4E Same as Unspecified Accuracy of Accuracy  $+/-32x10^{-6}$  $32x10^{-6}$ N/A 4 Synchronizing Same as Accuracy of Accuracy  $+/-32x10^{-6}$

Tabel 2.1. ANSI T1.101 Stratum Clock Level Requirements [8]

Namun pada kenyataannya, suatu jaringan tidak bisa mengalami keserempakan *clock* secara sempurna di setiap titik pada jaringan sinkronisasi. Hal ini dikarenakan adanya beberapa penyimpangngan penyimpangan dari *timing* ideal yang berupa *jitter, wander*, maupun *slip*. Dimana *slip* dapat terjadi apabila

terdapat posisi digit dari sinyal dijital mengalami kerusakan atau kehilangan dan juga mengalami penggandaan akibat aberasi proses sinkronisasi yang terjadi pada fasilitas transmisi ataupun *switching*.

#### 2.1.4 Sinkronisasi Antar Jaringan

Dalam memenuhi kualitas sinkronisasi yang handal dan memiliki performansi yang baik, maka yang patut diperhatikan adalah kondisi antar jaringan yang harus berjalan secara serempak. Hal ini ditujukan langsung dalam pengiriman pelayanan yang berupa layanan non-suara yang masih mengandalkan konektivitas dari ujung ke ujung (end to end). Yang mengharuskan mampu berjalan dan bekerja secara serempak.

Ada beberapa cara dalam menyerempakkan *clock* antar jaringan, diantaranya adalah dengan menyerempakkan *clock* secara utuh melalui satu jaringan dengan jaringan lainnya atau membuat jaringan beroperasi secara utuh dan serempak terhadap sumber clock yang menjadi titik acuan sinkronisasi.

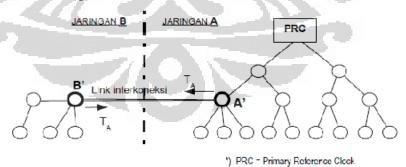

Gambar 2.8 menunjukkan ilustrasi mengenai jaringan sinkronisasi B diserempakkan secara utuh dengan jaringan sinkronisasi A. Dari gambar 2.8 terlihat bahwa hanya jaringan sinkronisasi A yang memiliki sumber *clock*, yakni *Primary Reference Clock* (PRC). Sedangkan untuk jaringan sinkronisasi B tidak memiliki acuan *clock*, untuk itu *Synchronization Supply Unit* (SSU) pada jaringan B diharuskan mencari sumber *clock* untuk menyerempakkan *Network Element* (NE) yang berada di tingkatan bawah.

Gambar 2.8 Sinkronisasi jaringan B dengan jaringan A [4]

Dengan melakukan interkoneksi dengan jaringan sinkronisasi A yang berada di sekitar jaringan sinkronisasi B, maka dengan menghubungkannya melalui *link* interkoneksi, gerbang interkoneksi dari *Synchronization Supply Unit* (SSU) pada jaringan sinkronisasi B dapat mengambil sinyal *timing* T<sub>A</sub> yang

berasal dari gerbang interkoneksi jaringan sinkronisasi A. Kemudian sinyal *timing* T<sub>A</sub> tersebut didistribusikan ke *Network Element* (NE) yang berada pada jaringan sinkronisasi B. Setelah semua *clock* terdistribusi secara menyeluruh, maka *Synchronization Supply Unit* (SSU) pada jaringan sinkronisasi B yang menjadi penghubung antara jaringan sinkronisasi A dengan B, kini menjadi sumber sinkronisasi *clock* . untuk meningkatkan tingkat kehandalan dalam sinkronisasi pada jaringan sinkronisasi B tersebut, maka interkoneksi pada jaringan sinkronisasi A dengan B dapat dilakukan melalui dua pasang sentral *gateway* [4].

Gambar 2.9 Sinkronisasi antar jaringan dengan acuan PRC [4]

Berbeda halnya dengan gambar 2.9 yang mengilustrasikan sinkronisasi antara jaringan A dengan B dengan acuan sinkronisasi dari *Primary Reference Clock* (PRC) masing-masing dengan akurasi frekuensi yang sama yakni 1x10<sup>-11</sup> [5]. Terlihat bahwa gambar 2.9 memakai konsep *plesiosinkronus* dimana selama kedua *Primary Reference Clock* (PRC) tersebut memiliki akurasi frekuensi yang sama, maka gangguan *slip* yang terjadi hanya sekali dalam 70 hari. (Rekomendasi ITU-T G.811 [7])

#### 2.2 Teknologi Sinkronisasi Masa Depan

Konsep *Next-Generation Network* (NGN) diterapkan untuk merealisasikan perkembangan industri telekomunikasi masa depan yang mengedepankan layanan multimedia bercirikan konvergensi dan optimasi jaringan. Konsep *Next-Generation Network* (NGN) juga ditujukan untuk melengkapi teknologi layanan berbasis paket IP sekarang ini diterapkan.

Definisi Next-Generation Network (NGN) menurut rekomendasi ITU Y.2001, Next-Generation Network (NGN) adalah jaringan berbasis paket yang mampu menyediakan berbagai layanan telekomunikasi, dapat mengintegrasikan teknologi broadband dan narrowband, menyediakan Quality of Service (QoS),

memiliki layer aplikasi yang *independent* terhadap layer *transport*, memungkinkan akses tanpa batas ke berbagai penyedia layanan dan mendukung mobilitas untuk menyediakan layanan dimana saja dan kapan saja bagi pengguna [9].

Gambar 2.10 Model Sinkronisasi Next Generation [10]

Arsitektur pada sinkronisasi *Next-Generation* menerapkan sistem distribusi yang lebih kompleks dalam sistem interkoneksi yang menerapkan model terdahulu. Dengan inilah diharapkan sinkronisasi masa depan dapat mengedepankan alokasi pemanfaatan serta efisiensi *bandwidth* dan meningkatkan performansi dalam hal kestabilan dalam pengiriman akurasi frekuensi dan kestabilan sinyal *timing* dan diharapkan mampu meminimalisir akan adanya gangguan-gangguan yang kerap terjadi pada jaringan paket.

Synchronous Ethernet (SyncE) dan IEEE 1588 v2 adalah dua buah macam contoh teknologi yang dipergunakan dalam konsep sinkronisasi masa depan [10]. Dimana kedua teknologi tersebut mengedepankan adanya tingkat kehandalan dan memberikan fitur yang bermanfaat untuk generasi mendatang.

#### BAB 3

#### SYNCHRONOUS ETHERNET DAN IEEE 1588V2

Ethernet merupakan salah satu teknologi yang paling banyak diminati untuk beberapa tahun terakhir. Biaya operasional yang cukup rendah, hirarki yang tidak terlalu rumit, dan pemakaian teknologi tersebut yang sudah menyeluruh oleh berbagai perusahaan telekomunikasi menjadi pertimbangan mengapa ethernet mengalami perkembangan yang sangat pesat.

Jaringan berbasis paket yang menggunakan transmisi secara asinkronus membuat banyak aplikasi layanan terdahulu seperti *circuit switched* dan *Wireless Backhaul* tidak dapat didukung. Hal ini dikarenakan karena beberapa layanan tersebut masih tergantung oleh adanya sinkronisasi.

Untuk itu, muncul solusi untuk mengatasi masalah tersebut, dengan diperkenalkannya *Synchronous Ethernet* (SyncE) dan IEEE 1588 v2 atau yang lebih dikenal dengan *Precision Time Protocol*) untuk menjamin adanya sinkronisasi melalui jaringan paket. Metode *Synchronous Ethernet* (SyncE) mengandalkan *physical layer* dalam pengiriman sinkronisasi yang menjamin atas kualitas frekuensi. Sedangkan IEEE 1588 v2 mengandalkan *Time Stamp* dalam sinkronisasi *clock* dengan menggunakan konsep hirarki *Master-Slave*.

#### 3.1 Synchronous Ethernet

#### 3.1.1 Konsep Dasar Synchronous Ethernet

Synchronous Ethernet (SyncE) adalah sebuah teknologi sinkronisasi yang mengandalkan Physical Layer (PHY). Sinyal clock Synchronous Ethernet (SyncE) berasal dari clock yang dibangkitkan oleh sumber clock Primary Reference Clock (PRC). Sama halnya dengan clock yang diimplementasikan pada jaringan SONET/SDH sehingga membuat adanya kesamaan akurasi frekuensi yang dimiliki kedua teknologi tersebut.

Tiap *node* yang diimplementasikan pada *Synchronous Ethernet* (SyncE), khususnya pada jaringan paket akan membentuk sebuah rantai sinkronisasi yang dapat berperan sepenuhnya dalam proses pemulihan *clock* maupun *timing* yang

berupa frekuensi yang berasal dari *node* pengirim dengan laju *upstream* dan kemudian didistribusikan hingga ke *node* penerima dengan laju *downstream* [1].

Dengan mengandalkan layer fisik, *Synchronous Ethernet* (SyncE) sangat kebal terhadap gangguan-gangguan yang terjadi dalam implementasi ke dalam jaringan paket, yang dapat berupa *Packet Delay Variation* (PDV). Hal ini dikarenakan *Synchronous Ethernet* (SyncE) hanya mendukung *timing* yang berupa frekuensi, bukan untuk fasa maupun *Time of Day* (ToD). Untuk itulah, *Synchronous Ethernet* (SyncE) sangat cocok diterapkan untuk mendapatkan hasil akurasi sinkronisasi frekuensi yang presisi.

#### 3.1.1.1 Konsep Distribusi Clock Pada Synchronous Ethernet

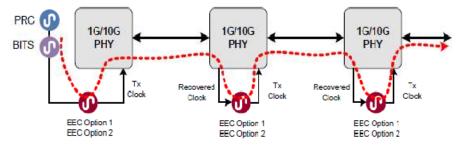

Gambar 3.1 Konsep distribusi *clock* pada *Synchronous Ethernet* [1].

Gambar 3.1 mengilustrasikan mengenai konsep distribusi *clock* antara tiga buah *node* dengan mengimplementasikan *Synchronous Ethernet* (SyncE) di dalamnya. Pada gambar 3.1, terlihat jelas bahwa jalur distribusi *data* disalurkan secara langsung tanpa melalui lapisan fisik pada OSI *layer*. Berbeda dengan *clock*, yang mendistribusikannya melalui lapisan fisik ditambah dengan bantuan *Synchronous Ethernet Digital Phase Lock Loop* (SyncE DPLL) untuk memfilter *clock* dari pengaruh *jitter* dan *wander*. Dengan melakukan distribusi *clock* pada lapisan ini, *clock* telah dipastikan kebal terhadap segala sesuatu gangguangangguan yang terjadi pada jaringan berbasis paket.

Mula-mula *clock* dibangkitkan oleh *Primary Reference Clock* (PRC) dan kemudian didistribusikan ke rangkaian *Synchronous Ethernet Digital Phase Lock Loop* (SyncE DPLL) untuk menyaring *clock* dari pengaruh *jitter* maupun *wander*. Sehingga, didapat sebuah *clock* murni dari rangkaian *Synchronous Ethernet*

Digital Phase Lock Loop (SyncE DPLL) yang dapat dinamakan sementara menjadi clock ethernet. Kemudian clock tersebut disalurkan hingga ke node akhir.

Proses distribusi *clock* sebenarnya sudah terekonstruksi ke dalam bentuk rantai sinkronisasi [11]. Maka, proses distribusi pada *node* pertama hingga akhir memiliki proses yang sama. Namun kelemahan dari rantai sinkronisasi itu sendiri adalah jika salah satu *node* mengalami modus asinkron, maka dampak yang akan terjadi adalah putusnya rantai sinkronisasi [11] sehingga *node* tersebut akan kehilangan catu referensi sehingga *node* tersebut berada dalam mode *holdover* [3]. 3.1.2 Implementasi *Synchronous Ethernet* (SyncE) pada Jaringan Telekomunikasi

Konsep *Synchronous Ethernet* (SyncE) pada gambar 3.1 dapat diterapkan untuk pengimplementasian *node* dengan jarak yang yang bervariatif. Yang harus diperhatikan adalah perancangan atas peletakkan *node* pada suatu jaringan telekomunikasi untuk mendapatkan kualitas *timing* yang terbaik dalam hal akurasi sinkronisasi frekuensi. Karena pada dasarnya, *node* tersebut saling membentuk rantai sinkronisasi sehingga mampu memulihkan serta mentransmisikan ulang *timing* maupun akurasi sinkronisasi frekuensi [11].

Gambar 3.2 Distribusi Frekuensi Sinkronisasi dengan Implementasi *Synchronous Ethernet* [11].

Node-node pada jaringan paket dengan Synchronous Ethernet (SyncE) harus besifat sinkron satu sama lainnya, bila ada salah satu node asinkron maka

efek yang terjadi adalah putusnya rantai sinkronisasi [11]. Maka dari itu penggunaan *node* lebih baik dipakai tidak melebihi dari 60 buah *node* [11].

Gambar 3.2 menunjukkan ilustrasi pendistribusian *clock* dari stratum 1 hingga ke sisi pelanggan. Dimana implementasi pada gambar 3.2 tersebut masih menerapkan jaringan SONET/SDH. Hal tersebut ditunjukkan oleh garis merah (*line Timing*) yang menunjukkan bahwa adanya koordinasi pengiriman *clock* dalam hal ini adalah akurasi sinkronisasi frekuensi antar *Network Element* (NE) SONET/SDH (ditunjukkan oleh garis merah *line timing* dari NE a-d).

Clock dibangkitkan oleh Primary Reference Clock (PRC) dan didistribusikan ke Synchronization Supply Unit (SSU) hingga sampai ke Network Element (NE). Pada Network Element (NE) b, clock dipisahkan ke dalam jaringan paket inti dimana teknologi Synchronous Ethernet (SyncE) diimplementasikan. Di dalam Jaringan inti inilah, apabila sinkronisasi frekuensi mengalami ketidakakuratan akibat adanya interferensi selama pendistribusian clock akan dipulihkan kembali sesuai dengan gambar 3.3.

Gambar 3.3 Distribusi Frekuensi Pada Synchronous Ethernet [10]

Awalnya *Clock* yang diterima oleh *Router* cenderung stabil, namun dalam pendistribusian pasti mengalami interferensi seperti *jitter* maupun *wander*, maka *router* selanjutnya akan menerima ketidakstabilan frekuensi tersebut hingga menemui *Synchronization Supply Unit* (SSU) terdekat untuk dibangkitkan kembali frekuensi-frekuensi yang hilang selama proses distribusi dan kemudian akan disinkronkan kembali dengan *router* sehingga mendapatkan kualitas sinkronisasi frekuensi yang sama dengan sinkronisasi frekuensi awal yang baru diterima dari sumber *clock*. Hal ini dapat diilustrasikan pada Gambar 3.3.

Konsep Distribusi sinkronisasi frekuensi pada *Synchronous Ethernet* (SyncE) memiliki persamaan tersendiri. Dimana yang membedakannya adalah pada jaringan SONET/SDH yang berperan adalah *Add-Drop Multiplexer* (ADM)

dan konsep distribusi sinkronisasi antara SONET/SDH dengan *Synchronous Ethernet* hampir menyerupai dapat diilustrasikan pada gambar 3.4. Hal ini akan mengakibatkan bahwa tingkat akurasi sinkronisasi frekuensi yang dimiliki *Synchronous Ethernet* (SyncE) memiliki kesamaan dan cenderung menyerupai Akurasi frkuensi sinkronisasi yang dimiliki jaringan SONET/SDH.

Gambar 3.4 Distribusi Frekuensi pada SONET/SDH [10]

Setelah *clock* yang dihasilkan oleh *Synchronous Ethernet* (SyncE) telah stabil, maka *Node Router* A dengan *Network Element* (NE) SDH/SONET B akan disinkronisasikan kembali sehingga memiliki sinkronisasi frekuensi yang serupa dengan *clock* awal. Sehingga keduanya dapat dipergunakan dalam koordinasi dengan *node-node* yang lainnya yang memungkinkan tidak adanya data *slips* yang diakibatkan proses *buffer overflow* maupun *underflow* [11]. Hal tersebut tidak akan mungkin dapat terlaksana, bila tidak tersedianya sinkronisasi frekuensi. Maka dari itulah, peran-peran antar *node* pada *Synchronous Ethernet* (SyncE) diperlukaan koordinasi satu sama lainnya. Pada dasarnya, jumlah *node-node* yang diimplementasikan tidak dibatasi, namun demi menjaga kualitas dari sinkronisasi frekuensi maka disarankan untuk membatasinya ke dalam 60 *node* [11] karena dengan pertimbangan antar *node* tersebut perlu diawasi karena saling membentuk rantai sinkronisasi sehingga diperlukan pengawan ekstra agar rantai sinkronisasi tidak terputus sehingga menggangu jalannya distribusi *clock* maupun pengawasan dari jalannya distribusi *clock* tersebut.

#### 3.2 IEEE 1588 v2

Standar IEEE menetapkan teknologi IEEE 1588v2 atau *Precision Timing Protocol* (PTP) sebagai teknologi yang diperuntukkan untuk sinkronisasi *clock* pada jaringan. IEEE 1588v2 tergolong unik, karena *Precision Timing Protocol* (PTP) dapat menyelesaikan tiga macam sinkronisasi sekaligus, yakni

sinkronisasi frekuensi, fasa dan *Time of Day* (ToD). Awalnya, *Precision Timing Protocol* (PTP) pertama kali diperkenalkan untuk mengatasi rendahnya tingkat akurasi sinkronisasi yang diterapkan oleh *Network Time Protocol* (NTP) dan tingginya biaya yang dikeluarkan bila menggunakan teknologi *Global Positioning System* (GPS). Oleh karena itu, dengan diterapkannya *Precision Timing Protocol* (PTP) sebagai solusi untuk jaringan berbasis paket, maka *Precision Time Protocol* (PTP) dengan mudah mengalami permasalahan-permasalahan yang sering terjadi pada jaringan berbasis paket, seperti *Packet Delay Variation* (PDV).

## 3.2.1 Konsep Dasar IEEE 1588v2

Dilihat dari penyebaran distribusi clock, IEEE 1588 v2 secara umum dibagi menjadi 2 macam, yakni: *Two Way Time Transfer* (TWTT) dan *Timing over Packet*.

# 3.2.1.1 *Two-Way Time Transfer (TWTT)*

Konsep yang digunakan oleh IEEE 1588 v2 adalah menerapkan konsep *Two-Way Time Transfer* (TWTT) dengan tujuan untuk mengimbangi paket *delay* (δ). Paket *delay* merupakan jarak antara waktu disaat *node master* memberikan perintah untuk meninggalkan *node master* dan hendak menuju dan diterima oleh *node slave*.

Gambar 3.5 menunjukkan bahwa konsep *Two-way Time Transfer* (TWTT) memperlihatkan adanya pertukaran pesan waktu antara *node master* dengan *node slave*. Sehingga, *node slave* dapat menentukan serta mengoreksi nilai *time offset* yang terjadi selama proses pengiriman [12]. Mula-mula *node master* memberikan sebuah pesan *SYNC* dan diterima oleh *node slave*. Waktu pengiriman pesan *SYNC* tersebut membutuhkan waktu sebesar T<sub>1</sub> sehingga jeda waktu yang dihasilkan sesaat sebelum pengiriman pesan *SYNC* diterima oleh *node slave* akan menimbulkan *delay* sebesar δ<sub>1</sub>. Selama pengiriman *SYNC*, *node master* juga mengirimkan pesan *Follow\_Up* dengan waktu sebesar T<sub>2</sub> dalam bentuk *timestamp*. Kemudian *node slave* akan memberikan responsi atas hasil sinkronisasi *clock* dalam bentuk pesan *Delay\_Req* dengan waktu T<sub>3</sub>. Sehingga adanya jeda waktu yang diberikan sesaat sebelum *node master* menerima responsi dari *node slave* dapat dikatakan sebagai *delay* δ<sub>2</sub>. Kemudian dalam bentuk

timestamp, clock akan diberikan sinyal responsi bahwa pesan Delay\_Req telah diterima oleh node master dalam bentuk Delay\_Resp dengan waktu sebesar T<sub>4</sub>.

Gambar 3.5 Konsep Two-Way Time Transfer (TWTT) pada IEEE 1588 v2 [12]

Time Offset dapat dicari dengan mengukur waktu yang diterima dan yang dikirim. Sehingga dapat dirumuskan dalam persamaan sebagai berikut:

$$\bar{\theta} = \frac{(T_2 - T_1) - (T_4 - T_3)}{2} \tag{3.1}$$

Delay pun dapat dicari dengan persamaan sebagai berikut:

$$Delay = \frac{(T_2 - T_1) + (T_4 - T_3)}{2}$$

(3.2)

Maka *error* yang terjadi dapat dicari akibat ketidaksimetrisan atara *delay* yang terjadi. Dengan persamaan sebagai berikut:

$$\theta_{error} = \theta - \bar{\theta} = \frac{\delta_1 - \delta_2}{2} = \frac{A}{2}$$

(3.3)

Perlu diperhatikan bahwa pada kenyataannya *delay* dan *offset* tidak tetap dan *delay* bersifat cenderung asimetris [13]. Karena konsep *Two-Way Time Transfer* (TWTT) inilah membuat IEEE 1588 v2 memperhatikan batasan-batasan dalam berbagai segi, seperti dilihat dari segi efek dalam tahap pengimplementasi IEEE 1588v2, segi skalabilitas, tingkat kebutuhan akan spesialisasi desain jaringan hingga dari segi data kuantitatif dan hasil akhir [14].

# 1. Dilihat dari segi efek [14]

Efek yang sering terjadi selama dalam tahap pengimplementasian pada jaringan telekomunikasi dapat berupa *Packet Delay Variation* (PDV) yang akan mempengaruhi kualitas kinerja dari IEEE 1588 v2 terhadap jaringan telekomunikasi sehingga akan mempengaruhi akan kualitas layanan suatu penyedia jaringan dan juga dari segi kecocokan teknologi IEEE 1588v2 yang memungkinkan adanya peng*upgrade*an dari versi-versi yang terbaharui, sehingga akan menimbulkan efek ketidakcocokan antara versi baru dengan versi yang sebelumnya.

# 2. Dari Segi Skalabilitas [14]

Bila dilihat dari segi skalabilitas, teknologi IEEE 1588 v2 memiliki kecenderungan dimana saat bertambahnya *protocol traffic* akan mempengaruhi tingkat kongesi yang terjadi. Tidak tertutup kemungkinan akan berpengaruh terhadap proses regenerasi atau proses pembangkitan paket timing hingga pendistribusian yang menambah nilai *delay timing*.

# 3. Kebutuhan akan spesialisasi desain jaringan [14]

Kebutuhan spesialisasi dalam penempatan Teknologi IEEE 1588 v2 dalam desain jaringan sangatlah dibutuhkan. Hal itu dikarenakan dalam merencang desain jaringan dengan mengimplementasikan IEEE 1588v2 didalamnya, harus memperhatikan letak-letak elemen utama hingga pendukung. Karena IEEE 1588v2 memiliki ketergantungan terhadap konsep penyebaran distribusi sinkronisasi dengan dilihat dari beberapa sisi seperti master, slave, konfigurasi protokol yang dipakai dan faktor efisiensi jaringan yang jelas berbeda dengan penyebaran antara yang satu dengan yang lainnya. Dimana adanya ketergantungan terhadap penyebaran di sisi s*erver, master, client, network traffic,* konfigurasi protokol, dan faktor efisiensi jaringan yang jelas berbeda dari penyebaran yang satu dengan yang lainnya.

#### 4. Dari segi data kuantitatif [14]

IEEE 1588 v2 memiliki beberapa perangkat protokol khusus dalam hal *time stamping* yang sangat diperdunakan dalam peningkatan performansi, sehingga data kuantitatif mengalami kekurangan dengan alasan *time stamp* sudah dirancang secara khusus oleh beberapa perangkat protokol tersebut.

#### 5. Dari segi Hasil Akhir [14]

Adanya perbedaan hasil akhir ini diakibatkan oleh *node slave* dimana dari penggunaan oscillator, serta algoritma yang dipakai akan mempengaruhi hasil akhir. Sehingga perlu dipertimbangkan secara khusus dan matang dalam merencanakan jaringan serta pemakaian jenis konsep pada *node slave*.

## 3.2.1.2 Konsep *Timing over Packet* (ToP)

Pada konsep distribusi *timingg clock* melalui jaringan berbasis paket, mula-mula *clock* akan dibentuk dalam paket-paket yang akan didistribusikan tanpa melalui lapisan fisik pada OSI *layer*. Gambar 3.6 menunjukkan sebuah ilustrasi distribusi *clock* dengan konsep *Timing over Packet* (ToP). Setelah *clock* dibentuk dalam paket-paket, *node master* akan mengirim paket tersebut ke dalam jaringan *Packet Switched*.

Gambar 3.6 Konsep Timing over Packet (ToP) [1]

Di dalam awan jaringan *Packet Switched* tersebut, pengiriman paketpaket berlangsung oleh *router* yang akan langsung ditujukan ke *node* tujuan.

Dengan konsep ini, memberikan sebuah keunggulan dimana Jaringan *Packet Switched* itu sendiri dapat mengefisiensi pemakaian *Bandwidth* itu sendiri. Hal itu dikarenakan bahwa, selama pendistribusian *clock* tidak melewati banyak *router* maupun *gateway*, karena *clock* akan dikirimkan langsung ke *node slave* dengan proses *routing* yang fleksibel. Setelah paket diterima oleh *node slave*, kemudian paket tersebut dipulihkan kembali serta dikembalikan ke dalam bentuk *clock* kembali dan siap disebarkan ke jaringan akses.

Konsep dasar yang lainnya adalah dengan memerhatikan tipe clock dan algortima yang akan dipergunakan. IEEE 1588v2 mendirikan hirarki *clock*

master-slave pada jaringan, dengan clock slave disinkronkan oleh grandmaster clock, hal ini serupa dengan sumber clock yang dibangkitkan oleh Primary Reference Clock (PRC). Dari segi konsep hirarki inilah, IEEE 1588v2 dapat memisahkan jaringan ke dalam beberapa wilayah dengan melihat satu clock grandmaster di tiap wilayah sebagai sumber clock untuk semua slave clock yang berada di wilayah tersebut. Ada empat tipe clock yang diperkenalkan oleh IEEE 1588v2, yakni Ordinary Clock, Boundary Clock, Transparent Clock, dan Management Node. [15]

# 1) Ordinary Clock

Dimana pada *Ordinary Clock*, *Precision Timing Protocol* (PTP) *clock* berhubungan dengan *Precision Timing Protocol* (PTP) satu *port*.

# 2) Boundary Clock

Dimana *Precision Timing Protocol* (PTP) *clock* berhubungan dengan lebih dari satu *Precision Timing Protocol* (PTP) *port* yang dapat bertindak sebagai *node master* dan *node slave*.

# 3) Transparent Clock

Dimana *Precision Timing Protocol* (PTP) *clock* mengirimkan semua pesan serta mengatur pesan tersebut untuk direfleksikan dengan pesan *Sync* maupun *Delay\_Req*. Sehingga pesan tersebut sampai hingga ke perangkat sinkronisasi.

#### 4) Management Node

Merupakan perangkat *Peer to Peer* (P2P) dihungkan dengan banyak *node*.

Algoritma Best Master Clock dipergunakan Precision Timing Protocol (PTP) untuk memilih clock dengan akurasi sinkronisasi yang memiliki kualitas baik. Algoritma tersebut membandingkan dataset dengan clock yang akan dipilih. Algoritma tersebut akan berusaha memilih clock dari grandmaster untuk menemukan jalur routing terbaik hingga menuju slave clock dan juga dapat memilih kualitas clock yang terbaik dari grandmaster yang ada.

#### 3.2.2 Implementasi IEEE 1588v2 pada Jaringan Telekomunikasi

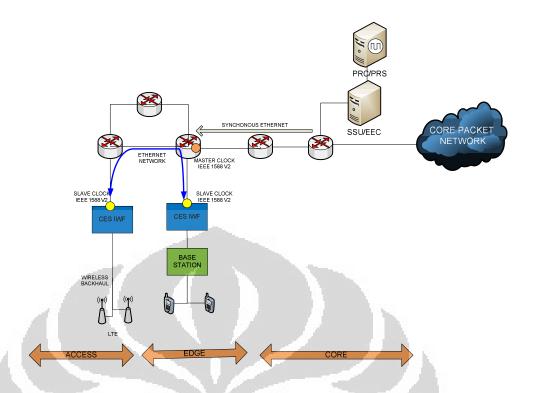

Distirbusi sinkronisasi *timing* pada IEEE 1588 v2 memiliki alur yang hampir serupa dengan alur *Synchronous Ethernet* (SyncE). Gambar 3.7 akan menunjukkan ilustrasi alur distribusi sinkronisasi *clock* dengan implementasi teknologi IEEE 1588 v2 di dalam jaringan inti. Mula-mula *clock* dibangkitkan oleh sumber *clock Primary Reference Clock* (PRC) dengan akurasi frekuensi sebesar 1x10<sup>-11</sup> yang ditetapkan oleh Rekomendasi ITU-T G.811 [7]. Kemudian *clock* tersebut didistribusikan hingga mencapai ke *Network Element* (NE) SONET/SDH yang membentuk sebuah *ring*. Hal ini bertujuan langsung terhadap proses penyerempakan *clock* antar *Network Element* (NE) SONET/SDH yang masih mendukung teknologi terdahulu.

Gambar 3.7 Distribusi *Timing* Berbasis Paket [11]

Dengan menerapkan tipe *clock* yang berupa *Boundary Clock*, [15] diharapkan mampu memperpendek jaringan yang berskala besar hanya dengan menggunakan konsep *Master-Slave* yang diterapkan pada IEEE 1588 v2. Kemudian clock tersebut akan terus dialirkan hingga ke *node slave*. Pada gambar 3.7 terlihat adanya dua buah pengimplementasian *node slave* yang mendukung teknologi *Wireless Backhaul* dan layanan yang masih menggunakan teknologi SONET/SDH. Maka dari itu, diperlukan adanya sinkronisasi *clock* antara *node slave* IEEE 1588v2 dengan *Network Element* SONET/SDH hingga mendapatkan

akurasi *timing* yang berkualitas untuk kemudian didistribusikan hingga ke jaringan akses.

Sehingga dapat ditarik sebuah analisis mengenai implementasi teknologi tersebut ke dalam jaringan telekomunikasi yaitu dengan menggunakan tiga macam sinkronisasi timing sekaligus, teknologi IEEE 1588 v2 sangat cocok diimplementasikan ke dalam jaringan 4G yang mengandalkan distribusi waktu serta dengan memakai konsep Master-Slave akan mengurangi implementasi node dari Network Element (NE) di dalam jaringan paket. Sehingga akan menghindari pemborosan biaya dalam proses pengupgradean peralatan switch maupun routing yang telah ada sebelumnya dan kemudian, dilihat dari proses monitoring antar Network Element (NE) akan semakin mudah karena node Network Element (NE) dipakai sangatlah sedikit yakni kurang dari 10 node yang [11].

#### **BAB 4**

# ANALISIS PERBANDINGAN ANTARA SYNCHRONOUS ETHERNET DENGAN IEEE 1588 V2

# 4.1 Tabel Perbandingan antara Synchronous Ethernet dengan IEEE 1588 v2

Berdasarkan penjelasan dari bab tiga tentang *Synchronous Ethernet* (SyncE) dan IEEE 1588v2 dapat dilakukan sebuah analisis dari parameter-parameter yang dibuat tabel berdasarkan parameter teknis dasar sinkronisasi yang ditunjukkan pada tabel 4.1

Tabel 4.1 Tabel perbandingan antara Synchronous Ethernet dengan IEEE 1588 v2

| Parameter      | Synchronus      | Score | IEEE 1588 v2      | Score |

|----------------|-----------------|-------|-------------------|-------|

| AU             | Ethernet        | (1-5) |                   | (1-5) |

| Timing Support | Frekuensi       | 4     | Frekuensi         | 5     |

|                |                 | -     | Fasa              |       |

|                |                 |       | Time of Day       | /     |

|                |                 | 1/    | (ToD)             |       |

| Kontinuitas    | Semua node      | 4     | Hanya <i>Node</i> | 4     |

| pada jalur     | harus mendukung |       | Master dan        |       |

| timing         | SyncE           |       | Slave yang        |       |

|                | U /             | 1 .   | mendukung         | 7     |

|                |                 |       | IEEE 1588v2       |       |

| Jumlah node    | Tidak dibatasi  | 3     | Dibatasi          | 5     |

| pada jalur     | (< 60 node)     | -     | (< 10 node)       |       |

| sinkronisasi 🖟 |                 |       |                   |       |

| timing         |                 |       |                   |       |

| Akurasi        | Sama dengan     | 5     | Lebih rendah      | 3     |

| Frekuensi      | SONET/SDH       |       | dari SyncE        |       |

| Konsep         | Rantai          | 3     | Konsep Master     | 5     |

| Sinkronisasi   | Sinkronisasi    |       | Slave             |       |

| Mendukung      | Ya              | 3     | Ya                | 5     |

| Teknologi 4G   |                 |       |                   |       |

| Total Nilai    |                 | 23    |                   | 27    |

#### Asumsi:

- 5 : Sangat Baik, untuk diimplementasikan

- 4 : Baik, dan perlu diperhatikan dalam beberapa hal

- 3: Cukup memuaskan

- 2: Kurang Memuaskan

- 1: Tidak Cocok untuk diimplementasikan

# 4.2 Analisa Perbandingan SyncE dengan IEEE 1588 v2

Analisis dilakukan atas dasar melihat tabel 4.1 dan diuraikan ke dalam beberapa parameter-parameter teknis yang akan dijelaskan sebagai berikut:

# 4.2.1 Timing Support

Pada Synchronous Ethernet (SyncE) hanya mendukung sinkronisasi frekuensi hal ini dikarenakan bahwa, Synchronous Ethernet (SyncE) bekerja penuh terhadap physical layer sehingga memiliki akurasi sinkronisasi frekuensi yang berkualitas tinggi. Karena tingkat akurasi frekuensi sangatlah dibutuhkan oleh jaringan akses dimana akan berpengaruh kepada kualitas layanan yang akan diterima oleh pelanggan. Dengan adanya penyerempakkan clock antar Network Element (NE) yang memakai teknologi Synchronous Ethernet (SyncE) diharapkan mampu mengatasi permasalahan jitter dan wander. Untuk itulah, demi menjaga kestabilan frekueni, peletakkan Network Element (NE) dengan Synchronization Supply Unit (SSU) perlu diperhatikan, karena untuk membuat sinyal yang diterima oleh Network Element (NE) agar tetap dalam keadaan stabil maka diperlukan catu clock tambahan yang diperoleh dari Synchronization Supply Unit (SSU) terdekat.

Keuntungan dari pemakaian *physical layer* itu sendiri adalah dipastikan bahwa tidak ada pengaruh terhadap *Packet Delay Variation* (PDV) dan mampu mengurangi efek *call overlap* hingga *slip* T1 yang sering terjadi pada penyebaran *clock* untuk komunikasi nirkabel. Namun kerugiannya adalah *clock Primary Reference Clock* (PRC) tersebut harus melewati banyak *router* serta *gateway* dari *Message Switching Centre* (MSC) atau *Central Office* (Kantor Pusat) menuju *cell* dari BTS itu sendiri sehingga tidak adanya kerusakan bila pada saat transmisi mengalami pertambahan *jitter* maupun *wander* [16].

Bila dibandingkan antara *Synchronous Ethernet* (SyncE) dengan IEEE 1588v2, teknologi IEEE 1588 v2 mengutamakan transmisi *timing* berdasarkan sinkronisasi frekuensi, fasa dan *Time of Day* (ToD). Dengan memakai konsep *Two Way Time Transfer* (TWTT), sinkronisasi fasa maupun frekuensi menjadi prioritas dalam menentukan *spectral efisiensi*. Fasa akan mempengaruhi ketidaksimetrisan dari pengiriman frekuensi sehingga ketidakefisiensi dari frekuensi tersebut, dapat mengurangi penggunaan spektrum hingga 85% ataupun lebih rendah dari itu. Hal ini dikarenakan bahwa frekuensi menjadi suatu tolak ukur dalam sisi akurasi *timing*. Sedangkan *Time of Day* (ToD) sangat diperlukan oleh operator dalam memenuhi kebutuhan operasional dalam hal *Billing* maupun *Service Level Agreement* (SLA).

Sehingga atas dasar tersebut, penilaian dari segi *timing support*, IEEE 1588 v2 terlihat unggul dalam memenuhi beberapa aspek dibandingkan SyncE, kerena pada IEEE 1588 v2 yang memiliki sinkronisasi *Timing* berupa *Time of Day* (ToD) memberikan suatu fitur *Billing* dan *Service Level Agreement* (SLA), dimana fitur aplikasi tersebut akan memberikan jaminan secara langsung dan transparan untuk manajemen *bandwidth* yang dinamis dimana *billing* merupakan sebuah kunci utama dalam memenuhi kepuasan konsumen. Dan dari sisi fasa dan frekuensi akan mempengaruhi dari sisi penggunaan spektrum itu sendiri. Dimana dengan meningkatkan efisiensi dari sinkronisasi frekuensi maupun fasa akan menekan biaya untuk penggunaan spektrum itu sendiri.

# 4.2.2 Kontinuitas pada jalur timing

Pada *Synchronous Ethernet* (SyncE) yang patut diperhatikan adalah dimana keseluruhan *node* yang berada pada jaringan distribusi sinkronisasi harus mendukung sepenuhnya peran dari *Synchronous Ethernet* (SyncE) itu sendiri. Dimana pada *Synchronous Ethernet* (SyncE), *node-node* pada *Network Element* (NE) akan membentuk sebuah rantai dengan *Primary Reference Clock* (PRC) yang akan digambarkan pada gambar 4.1

Gambar 4.1 Distribusi sinkronisasi pada PHY Ethernet. [11]

Hal ini terlihat bahwa antar *node* pada suatu jaringan distribusi sinkronisasi harus saling mendukung satu sama lain dan juga mendukung dari *Synchronous Ethernet* (SyncE) itu sendiri. Hal ini sangat berguna, dimana tiap *node* pada rantai sinkronisasi tersebut dapat mampu memulihkan dan mentransmisikan ulang sinkronisasi frekuensi tersebut. Hal ini sangat dibutuhkan oleh *Synchronous Ethernet* (SyncE) untuk mendapatkan sinkronisasi frekuensi yang berkualitas tinggi.

Sedangkan untuk IEEE 1588 v2 yang berperan serta adalah *node Master* dan *Slave*. Dengan memakai tipe *clock* yang berupa *Boundary Clock* [15] diharapkan mampu menyederhanakan jaringan yang tergolong besar menjadi ke beberapa bagian jaringan berkapasitas kecil (ditunjukkan oleh gambar 4.2).

Gambar 4.2 IEEE 1588 v2 Boundary Clock [17]

Pada gambar 4.2 terlihat bahwa *clock* yang dibangkitkan oleh *Grand Master Clock* yang bersumber kepada *Global Positioning System* (GPS) akan mendistribusikan *clock* tersebut hingga ke *client (slave clock)*. Namun pada saat transmisi tersebut *clock* pasti mengalami degradasi, untuk itu *Boundary clock*

#### **Universitas Indonesia**

akan memulihkan dan membangkitkan kembali *clock* tersebut sebelum disampaikan ke *client* (*slave clock*).

Router dan switch berupaya untuk menampilkan adanya perbedaan delay yang terjadi dalam proses transmisi maupun penerimaan paket yang berasaskan pola trafik sehingga dapat dikatakan adanya Packet Delay Variation (PDV) yang menjadi faktor batasan utama dalam hal untuk pengiriman akurasi frekuensi dan fasa melalui jalur timing yang sinkronus. Atas dasar inilah yang menyebabkan keterkaitan antara node master dan slave dibutuhkan.

Nilai yang diberikan untuk masing-masing adalah sama dengan atas dasar pertimbangan, bahwa *Synchronus Ethernet* (SyncE) maupun IEEE 1588 v2 sama sama memiliki kehandalan masing-masing namun yang terpenting adalah keduanya tersebut sama-sama untuk mengeliminasi maupun mengurangi pemakaian *node* pada jaringan tersebut dan juga spesifikasinya dalam hal *Packet Delay Variation* (PDV), *jitter* maupun *wander*.

# 4.2.3 Jumlah node pada jalur sinkronisasi timing

Pada dasarnya, *node* pada *Synchronus Ethernet* (SyncE) tidak dibatasi selama rantai sinkronisasi tetap terjaga, tidak mengalami putus serta tidak mengalami penyisipan *node* asinkron. Hal ini dikarenakan bahwa untuk mendapatkan sinkronisasi frekuensi yang berkualitas tinggi diperlukan perhatian penting terhadap *node* yang diimplementasikan. Untuk itu, demi menjaga kualitas frekuensi dan mencegah putusnya rantai sinkronisasi, *node* dibatasi kurang dari 60 *node* [11].

Pada IEEE 1588 v2, sesuai dengan konsep *boundary clock* yang menerapkan *master-slave* berupaya untuk memperkecil jumlah jaringan yang semula besar. Untuk itu jumlah *node* yang dipakai tidak lebih dari 10 *node* [11].

Nilai yang diberikan kepada IEEE 1588 v2 jauh lebih tinggi ketimbang nilai yang diberikan kepada *Synchronus Ethernet* (SyncE), hal itu berdasarkan atas pertimbangan efisiensi terhadap pengimplementasian *node* yang akan dipakai oleh *Network Element* (NE). Dengan memakai konsep *Master-Slave* diharapkan mampu mengurangi biaya implementasi terhadap pemakaian *Network Element* (NE). Dan selain itu pula dalam proses pengawasan atau *monitoring* antar

Network Element (NE) jauh lebih praktis ketimbang Synchronous Ethernet (SyncE). Karena jika salah satu node Synchronous Ethernet (SyncE) dalam kondisi asinkron, maka kondisi terburuk yang akan terjadi adalah putusnya rantai sinkronisasi sehingga distribusi sinkronisasi mengalami degradasi sehingga perlu adanya proses routing ulang yang akan menambah peluang terjadinya kongesi, jitter maupun wander.

#### 4.2.4 Akurasi Frekuensi

Akurasi Frekuensi untuk *Synchronous Ethernet* (SyncE) menunjukkan indikasi mengenai kondisi saat *oscillator* mengalami *mode holdover* pada saat hilangnya proses sinkronisasi (*loss of Synchronization*). *Synchronous Ethernet* (SyncE) memiliki kesamaan dengan akurasi sinkronisasi frekuensi SONET/SDH yang diatur pada rekomendasi ITU-T G.811 [7] yakni sebesar 1x10<sup>-11</sup> atau setara dengan akurasi sinkronisasi frekuensi pada *Primary Reference Clock* (PRC). Tabel 2.1 sebelumnya menjelaskan mengenai batasan toleransi slip dan akurasi sinkronisasi frekuensi.

Sedangkan Pada IEEE 1588 v2 memiliki akurasi frekuensi dibawah dari *Synchronous Ethernet*. Yang dimaksud disini adalah untuk akurasi stratum 1 pada IEEE 1588 v2 memiliki nilai berkisar 25 nanosekon.

Nilai yang diberikan untuk SyncE jauh mengungguli ketimbang IEEE 1588 v2 memiliki alasan yakni dengan adanya kesamaan antara akurasi sinkronisasi frekuensi *Synchronus Ethernet* (SyncE) dengan SONET/SDH memberikan keuntungan tersendiri dalam hal pemenuhan layanan yang terdahulu. Dengan adanya kesamaan seperti ini, tidak tertutup kemungkinan, layanan yang beroperasi membutuhkan sinkronisasi pada jaringan SONET/SDH akan terpenuhi seperti *layanan Wireless Backhaul*. Hal ini berbeda dengan IEEE 1588 v2 yang mengunggulkan sisi *time stamp* dibandingkan frekuensi.

#### 4.2.5 Konsep Sinkronisasi

Synchronous Ethernet (SyncE) tidak membutuhkan konsep master-slave layaknya IEEE 1588 v2, melainkan sudah terekonstruksi ke dalam bentuk rantai sinkronisasi [11]. Dimana telah disebutkan pada bab tiga bahwa antara *node* yang

satu dengan yang lain pada *Synchronus Ethernet* (SyncE) harus saling mendukung satu sama lain dengan *Synchronus Ethernet* (SyncE) itu sendiri. Hal ini dimaksudkan agar *node-node* tersebut tetap dalam keadaan sinkron dan tidak mengalami adanya *mode* asinkron.

Apabila hal tersebut terjadi, akan menyebabkan putusnya rantai sinkronisasi dan menyebabkan *clock* yang ditransmisikan tersebut tidak mengalami pemulihan ulang sehingga *clock* tersebut akan terpengaruh oleh adanya *jitter* dan *wander*. Sehingga tingkat akurasi sinkronisasi frekuensi pun akan berkurang dan mempengaruhi kualitas sinkronisasi frekuensi itu sendiri. Untuk itu pemantauan secara berkala untuk *node* patut diperhatikan.

Bila dibandingkan dengan *Synchronus Ethernet* (SyncE), konsep yang digunakan oleh IEEE 1588v2 adalah konsep *Master-Slave* yang akan membentuk *Boundary Clock* dan *transparent clock* [15]. Dimana konsep *boundary clock* itu sendiri berupaya untuk memberikan prioritas yang tinggi terhadap sinkronisasi paket dalam adanya pertukaran informasi antara *master* dengan *slave* sehingga *slave* akan meneruskan informasi tersebut. Hal ini bertujuan untuk memperbaiki sistem, skalabilitas jaringan dan akurasi *clock* sinkronisasi itu sendiri.

Transparant *clock* diperuntukkan untuk meringankan masalah performansi *clock*\_yang terjangkit oleh adanya *Packet Delay Variation* (PDV). Dengan konsep ini, *time stamp* pada IEEE 1588 v2 akan selalu diperbaharui di setiap *node* asinkron [11]. Hal ini bertujuan untuk mengimbangi adanya nilai *Packet Delay Vartiation* (PDV). Dengan kata lain, hal tersebut akan membuat adanya *delay* yang bervariatif sehingga akan terlihat secara transparan dalam artian terlihat jelas mekanisme distribusi yang dipakai. sehingga dapat meningkatkan akurasi sinkronisasi frekuensi maupun fasa. Namun kelemahannya adalah setiap *node* dalam jalur *timing* harus mendukung *protocol time stamping* terbaru dari IEEE 1588 v2.

Nilai yang diberikan IEEE 1588 v2 lebih unggul ketimbang *Synchronus Ethernet* (SyncE) Hal ini berdasarkan kepada dengan konsep yang dimiliki IEEE 1588 v2 yaitu konsep *Master-Slave* yang ditunjukkan pada gambar 4.2 akan mempermudah pengawasan dalam artian pengawasan terjadi dengan *mode server* dan *client*. Dimana dalam hal ini dapat menerapkan konsep sinkronisasi antara

client maupun server dengan sumber timing yang handal yang akan dibangkitkan oleh Grandmaster. Sehingga tingkat keakuratan time stamp antara client dan server dapat terjaga dengan baik.

# 4.2.6 Mendukung Teknologi 4G

4G atau yang dikenal dengan *Long Term Evolution* (LTE) adalah perkembangan lebih lanjut dalam hal komunikasi nirkabel. *Long Term Evolution* (LTE) itu sendiri mengedepankan *data rate* yang tinggi dimana nilai untuk *downlink* berkisar >1000 Mbps dan *Uplink* berkisar >50 Mbps dengan *Round Trip Delay* yang terjadi <10ms. Dengan *Long Term Evolution* (LTE) diharapkan untuk mengejar target kecepatan 3x HSPA. Hal ini untuk menunjang meningkatnya kebutuhan konsumen dalam hal layanan *Broadcast* seperti *gaming*, IPTV dan lainnya. Untuk menghadapi persiapan adanya *Long Term Evolution* (LTE), maka konsep sinkronisasi harus diperbaharui dengan diterapkannya *Synchronus Ethernet* (SyncE) dan IEEE 1588 v2 dalam pengimplementasiannya.

Bila *Synchronus Ethernet* (SyncE) diterapkan ke dalam jaringan 4G menjadi sebuah permasalahan yang kompleks dari segi kompabilitas jaringan seutuhnya, dikarenakan jaringan 4G mengutamakan *time stamp*. Namun tidak serta merta *Synchronus Ethernet* (SyncE) tidak menjadi sebuah pertimbangan untuk diimplementasikan, karena *Synchronus Ethernet* (SyncE) itu sendiri memiliki keuntungan tersendiri yakni tidak memiliki pengaruh terhadap *Packet Delay Variation* (PDV) maupun *paket loss* dan *latency* [3] yang disebabkan oleh distribusi berdasarkan waktu.

Dengan adanya transmisi *clock* melalui *physical layer* memberikan jaminan atas distribusi frekuensi untuk pengemasan sinyal untuk memenuhi performansi persyaratan jaringan tersebut. Terlebih lagi *Synchronus Ethernet* (SyncE) tidak memiliki batasan dalam hal skalabilitas, efisiensi dan lainnya yang diakibatkan oleh distribusi waktu yang dimiliki oleh IEEE 1588v2.

Jaringan *Long term Evolution* (LTE) membutuhkan adanya fleksibilitas pada distribusi *timing*. Hal ini otomatis mengarah kepada sinkronisasi, karena teknologi tersebut memiliki transmisi yang berbeda dengan sebelumnya. Selain itu pula yang menjadi pertimbangan adalah *Synchronus Ethernet* (SyncE) terbatas

dalam batasan operator jaringan. Untuk itulah, *Synchronus Ethernet* (SyncE) menjadi pertimbangan alasan mengapa teknologi ini kurang layak diimplementasikan kepada jaringan 4G.

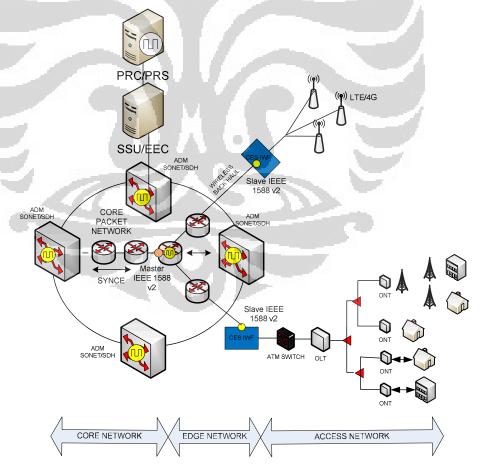

Berbeda dengan IEEE 1588 v2, teknologi ini sangat cocok dengan jaringan 4G yang mengedepankan solusi paket berbasis *end to end*. Terlebih lagi, bahwa IEEE 1588 v2 mulanya dirancang untuk menyediakan waktu yang presisi untuk aplikasi industri, namun kini digunakan untuk jaringan *wireless backhaul* dengan tingkat akurasi waktu dan frekuensi yang handal. Dengan memakai *Timing* berbasis paket, memiliki kemampuan untuk mentransmisikan keduanya tidak hanya sinkronisasi frekuensi saja melainkan ditambah dengan informasi fasa dimana sangat cocok diterapkan pada aplikasi jaringan *Wireless* (seperti *Long term Evolution* (LTE), Wimax, W-CDMA).